SLC to CompactLogix

Programming Migration

Bulletins 1746, 1747, 1769, 5069

Application Profile

Original Instructions

2 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

SLC to CompactLogix Programming Migration Application Profile

Important User Information

Read this document and the documents listed in the additional resources section about installation, configuration, and

operation of this equipment before you install, configure, operate, or maintain this product. Users are required to familiarize

themselves with installation and wiring instructions in addition to requirements of all applicable codes, laws, and standards.

Activities including installation, adjustments, putting into service, use, assembly, disassembly, and maintenance are required to

be carried out by suitably trained personnel in accordance with applicable code of practice.

If this equipment is used in a manner not specified by the manufacturer, the protection provided by the equipment may be

impaired.

In no event will Rockwell Automation, Inc. be responsible or liable for indirect or consequential damages resulting from the use

or application of this equipment.

The examples and diagrams in this manual are included solely for illustrative purposes. Because of the many variables and

requirements associated with any particular installation, Rockwell Automation, Inc. cannot assume responsibility or liability for

actual use based on the examples and diagrams.

No patent liability is assumed by Rockwell Automation, Inc. with respect to use of information, circuits, equipment, or software

described in this manual.

Reproduction of the contents of this manual, in whole or in part, without written permission of Rockwell Automation, Inc., is

prohibited.

Throughout this manual, when necessary, we use notes to make you aware of safety considerations.

Labels may also be on or inside the equipment to provide specific precautions.

WARNING: Identifies information about practices or circumstances that can cause an explosion in a hazardous environment,

which may lead to personal injury or death, property damage, or economic loss.

ATTENTION: Identifies information about practices or circumstances that can lead to personal injury or death, property

damage, or economic loss. Attentions help you identify a hazard, avoid a hazard, and recognize the consequence.

IMPORTANT

Identifies information that is critical for successful application and understanding of the product.

SHOCK HAZARD: Labels may be on or inside the equipment, for example, a drive or motor, to alert people that dangerous

voltage may be present.

BURN HAZARD: Labels may be on or inside the equipment, for example, a drive or motor, to alert people that surfaces may

reach dangerous temperatures.

ARC FLASH HAZARD: Labels may be on or inside the equipment, for example, a motor control center, to alert people to

potential Arc Flash. Arc Flash will cause severe injury or death. Wear proper Personal Protective Equipment (PPE). Follow ALL

Regulatory requirements for safe work practices and for Personal Protective Equipment (PPE).

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 3

Table of Contents

Preface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

About This Publication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Studio 5000 Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Download Firmware, AOP, EDS, and Other Files . . . . . . . . . . . . . . . . . . . . 7

Summary of Changes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Chapter 1

Overview Why Convert . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

What Is Needed. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Download the Integrated Architecture Builder . . . . . . . . . . . . . . . . . . 9

SLC EtherNet/IP Adapter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1747-AENTR Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1747-AENTR and Rack Optimization. . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Exclusive Owner, Input Only, Listen Only, and None

Connection Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Add I/O Modules Online. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Using the 1747-AENTR Module in a Redundant Logix System . . . . 12

PLC-5/SLC 500 Architecture to Logix Architecture Comparison. . . . . . 12

SLC to Logix Memory Comparison. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Scan Time Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Local Rack SLC 500 I/O Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Remote Rack SLC I/O Modules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Overall Performance Expectations . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Logix Controller Boot Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Synchronous Versus Asynchronous I/O Scans . . . . . . . . . . . . . . . . . . 15

SLC I/O Local and Remote Rack Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Keeping I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Chapter 2

Migration Considerations Define Future Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Device Level Ring Topologies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Using DeviceNet Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Use of Advanced Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Communication with SLC Controllers Over Serial Networks. . . . . 18

Power Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Using Integrated Architecture Builder to Plan Hardware Migration. . 19

Replace Only the Local SLC Controller . . . . . . . . . . . . . . . . . . . . . . . . . 19

Replace the Local SLC System with CompactLogix System. . . . . . . 26

Adding a Chassis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Network Connection Options for the Remote (SLC System)

I/O Chassis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Create Project Bill of Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Table of Contents

Chapter 3

Conversion of Programs Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Download the Standalone RSLogix 500 . . . . . . . . . . . . . . . . . . . . . . . . 39

What to Expect from the RSLogix Project Migrator . . . . . . . . . . . . . 41

Application Code Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Convert RSLogix 500 Projects Into Studio 5000 Projects . . . . . . . . . . . . 44

Resolve the Differences in the New Logix Program . . . . . . . . . . . . . . . . . 47

SLC Controllers Data Tables and Logix Controller Tags. . . . . . . . . . 48

Resolve Program Code Issues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Work with PCE Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Locate PCE Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Recognize Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Resolve PCE Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Work with UNK Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Common PCE Issues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Map PLC/SLC Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Map I/Os . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Resolve Issues with Physical I/Os . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

MOV Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

CPS Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Alias Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Complete the MSG Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Replace SLC Processor and Adapters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Set the Network Address Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Determine Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

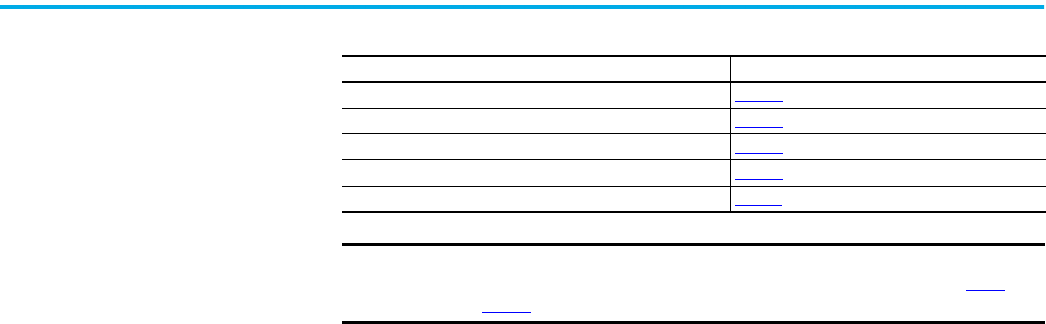

Install the Adapter Module in the Chassis . . . . . . . . . . . . . . . . . . . . . . 58

Connect Your Adapter to the Ethernet/IP Network through

RJ45 Connection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Replace Other Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Other Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Chapter 4

Convert Program Structures Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Divide Logic Into Tasks, Programs, and Routines . . . . . . . . . . . . . . . . . . 63

Create Continuous Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Create Event Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Create Periodic Tasks for Selectable Timed Interrupts (STIs) . . . . . . . . 64

Convert Input Interrupts (Dlls/Plls). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

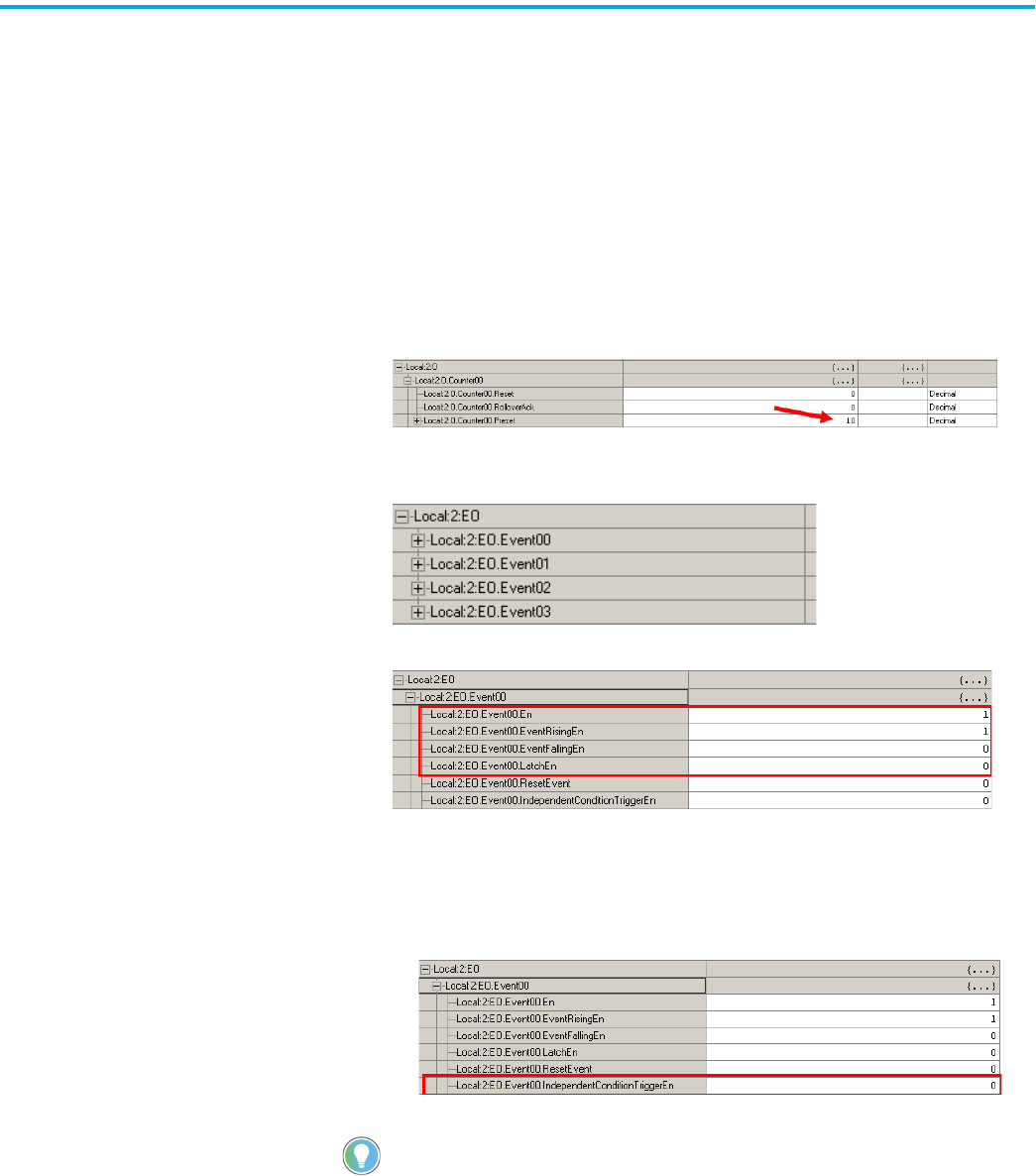

Interrupt Trigger by Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Interrupt Trigger by Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Create a Status File. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Appendix A

Program Conversion Errors

(PCE) Messages

Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 5

Table of Contents

Appendix B

I/O Modules Supported I/O Modules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Unsupported I/O Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Appendix C

Performance Expectations Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Appendix D

Advanced Modules Use Advanced Modules in a Logix System . . . . . . . . . . . . . . . . . . . . . . . . . 81

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

6 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Table of Contents

Notes:

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 7

Preface

About This Publication

This document focuses on converting an SLC™ program to a Logix program

and migrating the existing SLC I/O to an Ethernet network thereby helping to

leverage the existing I/O and minimize cost and risk. This document can be

used in the planning stages to help identify issues so that you can anticipate

the work that is involved in the conversion. The ideas that are presented in this

document require Studio 5000 Logix Designer® software version 21 or later

and RSLinx® software version 2.59 or later.

This document focuses on converting an existing SLC program to a

CompactLogix™ 5380 controller or CompactLogix 5370 controller. If you want

to convert your SLC program to a ControlLogix® 5580 controller or

ControlLogix 5570 controller the process is similar to what is presented in this

manual.

For information on migrating SLC™ 500 hardware to CompactLogix 5380

controller and Compact 5000™ I/O or CompactLogix 5370 controller and

Compact I/O™, see the SLC 500 Hardware Migration Reference Manual,

publication 1746-RM003

.

Studio 5000 Environment

The Studio 5000® Engineering and Design Environment combines

engineering and design elements into a common environment. The first

element in the Studio 5000 environment is the Logix Designer application. The

Logix Designer application is the rebranding of RSLogix 5000® software and

will continue to be the product to program Logix 5000™ controllers for

discrete, process, batch, motion, safety, and drive-based solutions.

The Studio 5000 environment was introduced in version 21.

The Studio 5000 environment is the foundation for the future of Rockwell

Automation engineering design tools and capabilities. The Studio 5000

environment is the one place for design engineers to develop all elements of

their control system.

Download Firmware, AOP,

EDS, and Other Files

Download firmware, associated files (such as AOP, EDS, and DTM), and access

product release notes from the Product Compatibility and Download Center at

rok.auto/pcdc

.

8 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Preface

Summary of Changes

This publication contains the following new or updated information. This list

includes substantive updates only and is not intended to reflect all changes.

Additional Resources

These documents contain additional information concerning related products

from Rockwell Automation.

You can view or download publications at r

ok.auto/literature.

Topic Page

Removed mention of MicroLogix™ 1500 migration 7

Updated screen captures of Integrated Architecture Builder 17

Replaced section on Power Consideration with link to 1746-RM003 19

Removed MicroLogix 1500 appendix 82

Resource Description

SLC 500 Hardware Migration Reference Manual, publication 1746-RM003

. Provides guidelines for migrating SLC 500 to CompactLogix or Compact 5000 hardware.

SLC Ethernet Adapter User Manual, publication 1747-UM076

Reference guide for the EtherNet/IP Adapter Module.

SLC Ethernet Adapter Installation Instructions, publication 1747-IN521 Installation instructions for the EtherNet/IP Adapter Module.

Converting PLC-5 or SLC 500 Logic to Logix5550 Logic Reference Manual,

publication 1756-RM085

Information on converting a PLC-5 or SLC 500 Logic to Logix5550®.

CompactLogix 5380, Compact GuardLogix 5380, and CompactLogix 5480

Controllers Specifications Technical Data, publication 5069-TD002

Provides CompactLogix, Compact GuardLogix, and CompactLogix controllers specifications.

CompactLogix 5380 Controllers User Manual, publication 5069-UM001

Describes how to install, use, and troubleshoot CompactLogix 5380 controllers and Compact

GuardLogix 5380 controllers.

Compact 5000 I/O Modules and EtherNet/IP Adapters Technical Data,

publication 5069-TD001

Provides Compact 5000 I/O and EtherNet/IP adapter specifications.

Compact 5000 I/O Serial Module User Manual, publication 5069-UM003

Describes how to install, use, and troubleshoot a Compact 5000 I/O serial module.

CompactLogix 5370 Controllers User Manual, publication 1769-UM021 Describes how to install, use, and troubleshoot CompactLogix controllers.

CompactLogix Controllers Specifications Technical Data, publication 1769-

TD005

Provides CompactLogix controllers specifications.

Converting PLC-5 or SLC 500 Logic to Logix based Logic, publication 1756-

RM085

Provides guidelines for migrating PLC-5 or SLC 500 programming to Logix based

programming.

Industrial Automation Wiring and Grounding Guidelines, publication 1770-4.1 Provides general guidelines for installing a Rockwell Automation industrial system.

Product Certifications website, rok.auto/certifications

. Provides declarations of conformity, certificates, and other certification details.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 9

Chapter 1

Overview

Why Convert Migration solutions help you to achieve increased productivity and lessen your

risk of maintaining your legacy equipment. Work with a supplier that has the

product, service, and industry knowledge to partner with you on an upgrade

strategy that will help you maximize your competitive advantage. Rockwell

Automation works with you to outline a plan to accomplish the following:

• Lower conversion time and labor costs

• Reduce risk by preserving existing field wiring connections

• Lower engineering costs

• Minimize production downtime

What Is Needed You need the following items for your migration project:

• Current SLC 500 control system

•CompactLogix Controller

• 1747-AENTR SLC EtherNet/IP™ Adapter (If you want to retain your

existing SLC I/O)

•Software

- Studio 5000 Logix Designer application version 30 or higher

-RSLogix 500® version 12

- Integrated Architecture® Builder (IAB)

Download the Integrated Architecture Builder

1. Go to http://www.rockwellautomation.com.

2. Mouse over the Support tab and click Selection and Configuration

.

3. Scroll down to the 'Control Systems Configuration Tools' section and

click 'Get Started’.

10 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 1 Overview

4. Scroll down to the Integrated Architecture Builder section and click

‘Download Now’.

The PSTInstallLite_2020.05.exe file pops up at the bottom of the screen.

5. Click Run.

The tool is installed on your computer.

6. Go to Start > Program > Rockwell Automation > Integrated Architecture

Builder to Run IAB.

SLC EtherNet/IP Adapter The 1747-AENTR adapter module enables CompactLogix and ControlLogix

processors to control SLC I/O modules. The adapter is primarily designed to

enable migration of existing SLC-controlled systems to Logix-based systems.

The adapter mainly acts as a gateway between the SLC backplane and

EtherNet/IP. It typically replaces an SLC controller in the SLC rack and

upgrades the remote SLC to EtherNet/IP.

Control of the backplane I/O is accomplished with a CompactLogix or

ControlLogix controller communicating through an EtherNet/IP router in the

Logix backplane, across EtherNet/IP, and into the 1747-AENTR gateway.

As a gateway between the SLC backplane and EtherNet/IP, the 1747-AENTR

module is a CIP™ server (for both Explicit Messaging and I/O) on the Ethernet

port, and an SLC host on the SLC backplane.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 11

Chapter 1 Overview

Connections can be made to supported SLC analog, digital, and specialty I/O

modules installed in the backplane.

1747-AENTR Connections

Exclusive Owner, Input Only, and Listen Only connections are Class 1

connections. The 1747-AENTR module supports a combined total of 96 Class 1

connections:

• One Exclusive Owner connection per slot

• A combination of five Input Only or Listen Only connections per slot

The 1747-AENTR module supports a maximum of eight Class 3 connections.

Class 3 connections are typically a connected ladder-triggered MSG

instruction to the 1747-AENTR module.

1747-AENTR and Rack Optimization

A major difference between using the 1747-AENTR adapter with SLC I/O

modules and any other Logix compatible I/O system is that the 1747-AENTR

adapter does not support a rack-optimized connection type. This means that

each module is an individual connection to the controller. These connections

must be taken into account when converting the SLC controller. The main

considerations are the effect on the Logix controller's total number of

connections and the allowable RPIs to the modules in the 1747-AENTR chassis.

Exclusive Owner, Input Only, Listen Only, and None Connection Types

People familiar with SLC programing and I/O may not be familiar with how

Logix handles programming and I/O. In simple terms, all I/O in a Logix

controller is placed in an I/O tree. All I/O modules in the I/O tree can have

multiple types of connections that transfer the I/O data into the Logix

controller's memory. Below are some basic definitions of the types of

connections that can be made to various SLC I/O modules.

• None – A method of establishing communication to a 1747-AENTR

module that enables connection to individual modules within the

1747-AENTR module chassis by using individual connections. After a

None connection is configured to a 1747-AENTR module, each module

that you desire to communicate through this connection must also be

configured under the 1747-AENTR module by using any type of

individual module connection (Exclusive Owner, Input Only, or Listen

Only). Only the 1747-AENTR module supports a None connection type. A

None connection does not affect the 96 total available Class 1 I/O

connections on the 1747-AENTR module.

• Exclusive Owner – There can be only one Exclusive Owner connection to

each module. The Exclusive Owner connection is the only connection to

send configuration data to that module. An Exclusive Owner connection

to a device is the only connection that determines the mode (Prog or

Run) of that particular device. Each Exclusive Owner connection does

IMPORTANT

See Appendix B for a list of supported and unsupported I/O modules.

12 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 1 Overview

subtract 1 from the 96 total available Class 1 I/O connections on the 1747-

AENTR module.

• Input Only – There can be as many as five Input Only connections to the

same module. This connection type lets multiple Logix controllers

receive incoming data from the same I/O module. If the connection is to

an I/O device that requires configuration or output data, the Input Only

connection does not send any configuration or output data. You can get

Input Only data with or without an existing Exclusive Owner connection.

Each Input Only connection subtracts one from the 96 total available

Class 1 I/O connections on the 1747-AENTR module.

• Listen Only – There can be as many as 5 Listen Only connections to the

same module. This connection type is identical to an Input Only

connection with two differences:

- Either an Exclusive Owner or Input Only connection must exist and be

working to the I/O module before a Listen Only connection can work.

- The Exclusive Owner or Input Only connection and the Listen Only

connection must all be set to Multicast. Each Listen Only connection

subtracts 1 from the 96 total available Class 1 I/O connections on the

1747-AENTR adapter.

Add I/O Modules Online

RSLogix 5000 software, version 15.02.00 and later, or Studio 5000

environment, version 21.00.00 and later, the 1747-AENTR module, and all

supported SLC I/O modules support adding I/O modules online and Module

Discovery. However, this feature is supported only in ControlLogix 5580 and

5570 controllers. CompactLogix 5380 and 5370 controllers do not support

adding I/O modules online or Module Discovery.

Using the 1747-AENTR Module in a Redundant Logix System

The 1747-AENTR is not compatible for use in a ControlLogix redundant system

using a 1756-SRM, 1756-RM, or 1756-RM2.

PLC-5/SLC 500

Architecture to Logix

Architecture Comparison

The following table shows the differences between PLC-5®/SLC 500 and

Logix architectures.

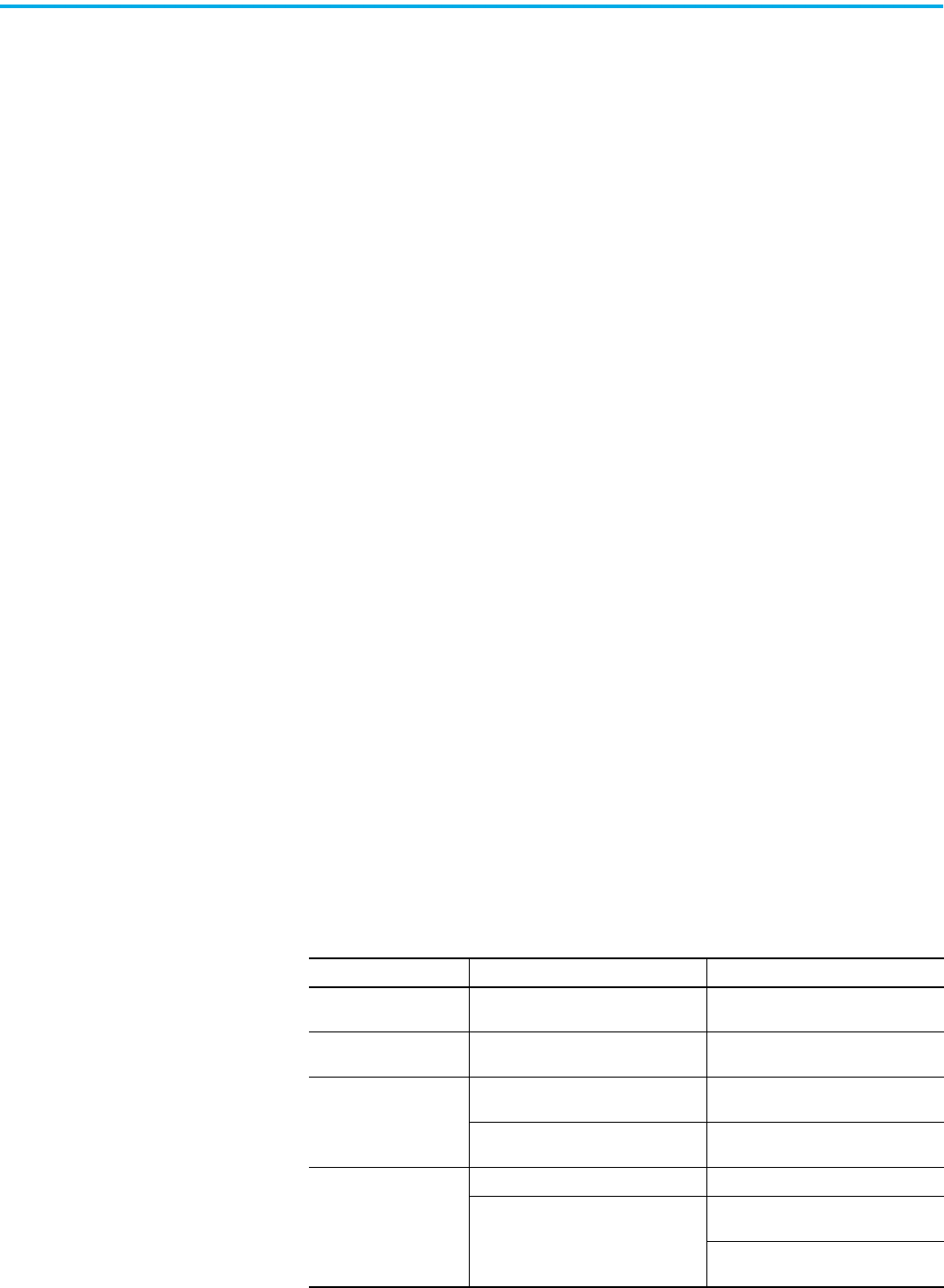

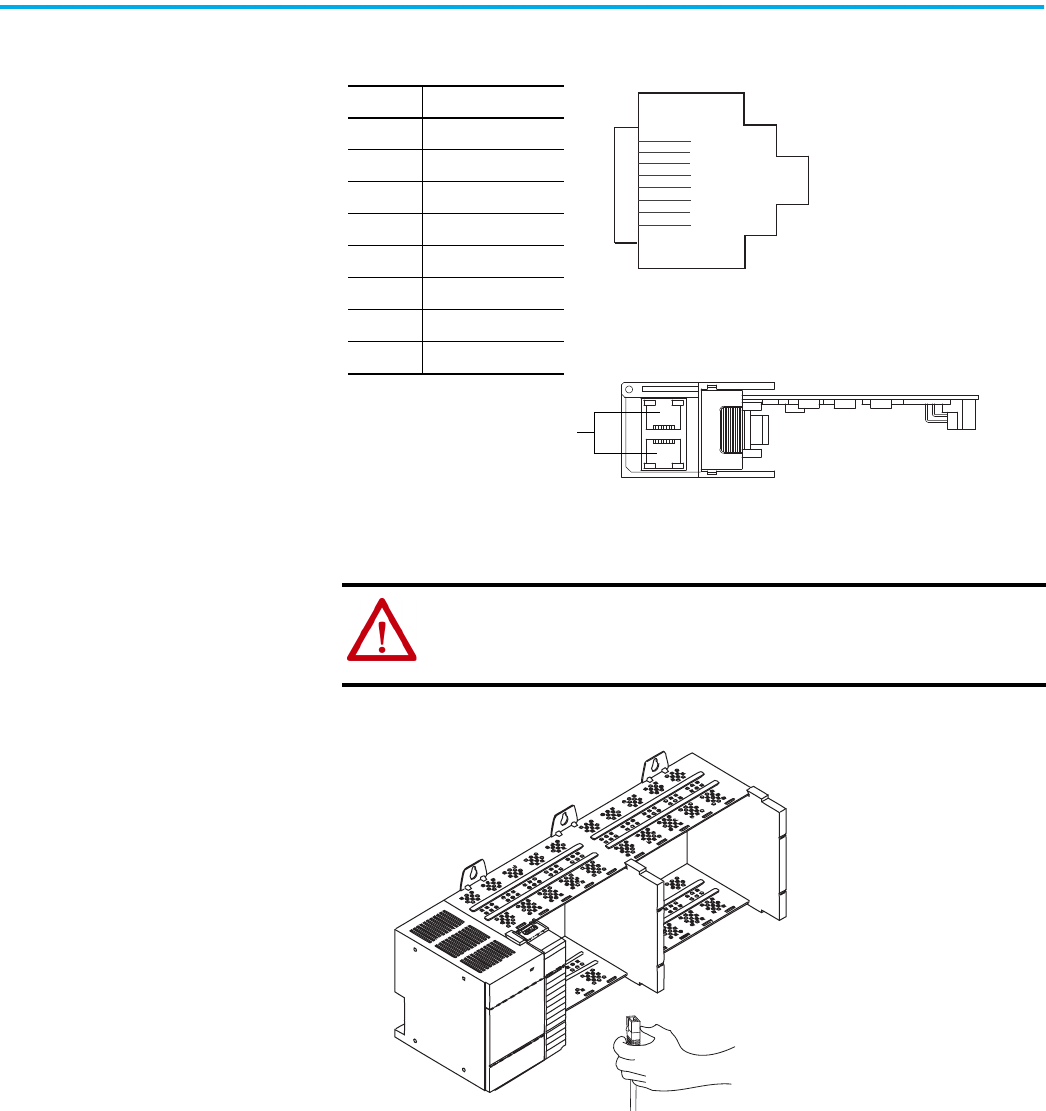

Attribute PLC-5/ SLC 500 Controller CompactLogix 5380 Controller

CPU

The SLC 500 processor is based on 16-

bit operations

Logix controllers use 32-bit operations

Operating system Process codes based on program files

Process codes based on tasks,

programs, and routine organizations

Inputs and Outputs (I/Os)

I/Os are mapped into I and O data table

I/O tags are automatically generated

whenever they are created

I/O data is updated synchronously to the

program scan

I/Os are updated asynchronously to the

logic scan

Data

Store data in global data table Support local and global data

Data are store in table format

Data is shareable with other Logix

Controller

Use array tables to store data in table

format

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 13

Chapter 1 Overview

SLC to Logix Memory

Comparison

When choosing a Logix controller to migrate to, you must consider the

memory size of your existing SLC program and in what type of Logix controller

the program will fit after conversion. SLC maximum memory sizes vary from 1

KB to 64 KB. Logix controllers vary in maximum memory size from about 380

KB to about 10 MB. While no two SLC programs' memory usage before and

after conversion is the same, a good rule of thumb is that a full 32 KB SLC

program converts to a Logix program size of about 360 KB. So in general, SLC

programs of less than 32 KB fit into any type of Logix controller while a full 64

KB SLC program fits only in Logix controllers with at least about 800 KB of

memory.

Scan Time Comparison The Logix controller has a significant advantage over the SLC controller in

regard to program scan time. While each situation is unique, it is likely that

you will see a reduction in overall scan time when you convert to a

ControlLogix 5580 or 5570 controller or a CompactLogix 5380 or 5370

controller. In many cases a scan time reduction is beneficial, but there can be

instances where this is not ideal and can disrupt an existing process. Consider

this in your conversion process and make the necessary adjustments to scan

time as needed.

While some conversions involve converting a single SLC controller to a single

Logix controller, there are cases where you want to convert multiple SLC

controllers and combine them into a single Logix controller. With the

significant decrease in scan time, this can be possible without any decrease in

throughput or performance.

After the conversion, you could expect a decrease of 50…80% in overall

program scan when running in a Logix controller as compared to an SLC

controller. For more information on converting an SLC 500 program, refer to

the Converting PLC-5 or SLC 500 Logic to Logix based Logic,

publication 1756-RM085

.

Local Rack SLC 500 I/O Modules

SLC I/O modules contained within the same chassis as the SLC 500 controller

are considered local I/O. In simple terms, the SLC controller can be removed

Time bases

Time is based on 16-bit architecture Time is based on 32-bit architecture

They can have different time bases (10

ms, 1 s)

Supports 1 ms time base

Communication

PLC-5 processor supports the following:

• Block-transfer read and write (BTR

and BTW) instructions

• ControlNet I/O (CIO)

• Message (MSG) instructions

MSG instructions

SLC 500 supports the following:

• Block-transfer read and write (BTR

and BTW) instructions

• Message (MSG) instructions

Attribute PLC-5/ SLC 500 Controller CompactLogix 5380 Controller

14 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 1 Overview

and a 1747-AENTR installed in its place. It is important to note that SLC local

I/O, both analog and discrete, was scanned fairly quickly, with the major

contributor to throughput being program scan.

See Appendix C

for information on performance expectations.

Remote Rack SLC I/O Modules

Many SLC systems have I/O remotely located from the SLC 500 controller. The

I/O can be scanned by a 1747-SCNR (ControlNet®) module or a 1747-SN (RIO)

module. The adapters used can be a 1747-ACNR (ControlNet) module or a 1747-

ASB (RIO) module. The 1747-SCNR/1747-SN modules scan I/O and place the

data in a combination of I1 Input, O0 Output, M1 Input, and M0 Output files.

Because the 1747-SCNR module and the 1747-SN module are not supported,

they are removed from the converted system and the 1747-ACNR module and

the 1747-ASB module are replaced with a 1747-AENTR module and scanned

directly by the Logix controller. After the replacement of the various modules

the data must be MOVed/COPied to/from the original I1, O0, M1, and M0

locations to the new Logix tag locations. The exact process of these moves is

beyond the scope of this document.

The scanning of the remotely located I/O in the SLC system was at a slower rate

than the scanning of local SLC I/O. After conversion to a Logix system, the scan

rate of the remote I/O scanned on Ethernet via the 1747-AENTR module will be

similar to that of the original SLC system.

Some SLC systems can perform Block Transfer Reads (BTR) and Block

Transfer Writes (BTW) over remote I/O via the 1747-SN module. This is a

specialized function and requires a more detailed description. The 1747-

AENTR module does not support the 1747-SN module, but the racks

communicated with by the 1747-SN module contain a 1747-ASB module that

can be replace by a 1747-AENTR module. If your existing SLC system is using

BTR and BTW instructions over remote I/O via the 1747-SN module, the BTR/

BTW can be replace by a module connection in the Logix Designer application.

Expect this part of the conversion to take additional work and time.

Overall Performance Expectations

While each conversion situation is unique, it is likely that the scanning of I/O

could be slower in a Logix system while the program scan is faster. Overall

performance and throughput are likely to be better than the existing system.

If the current system has stringent performance characteristics, we

recommend you perform a more detailed performance analysis to verify the

Logix performance in advance of your migration.

IMPORTANT

Modules requiring G-file configurations cannot be in a remote rack to a

Logix controller.

IMPORTANT

See Appendix B for a list of supported and unsupported I/O modules.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 15

Chapter 1 Overview

Logix Controller Boot Time

As Rockwell Automation moves forward with technology and adds more

functionality into the controllers, boot time can be affected. Here are some of

the reasons:

• More tasks are performed at startup, such as: memory validity checks,

safety diagnostics, controller health, and security tests.

• As memory sizes increase, so does the power required to back up that

memory.

• The controller does not enter the ‘RUN’ condition until there is enough

energy stored to tolerate a potential loss of power. Larger capacitors

require longer charge-up times.

• Certification requirements continue to drive more startup diagnostics

and code validation.

• SLC 500 processors power-up times were relatively small, taking only

several seconds. Some Logix controllers can take as long as 40 seconds to

power up.

Therefore, you can expect the boot time in the Logix controllers to be greater

than in your SLC controllers.

Synchronous Versus Asynchronous I/O Scans

The SLC 500 processor maps I/O data into Input and Output data table files.

The I/O data is updated synchronously to the program scan so you know you

have current values each time the processor begins a program scan and that

the I/O data does not change during the program scan. A Logix controller

references I/O that is updated asynchronously to the logic scan.

If you must maintain I/O data integrity throughout the program scan and/or

you must maintain synchronous I/O data transfers in the Logic controller you

must use a CPS copy instruction. See Knowledgebase answer ID 50235

for

more information on how to use the CPS instruction.

SLC I/O Local and Remote

Rack Size

The SLC 500 systems had a maximum single-chassis size of 13 slots, by using

various cables, multiple chassis could be connected together to create an

I/O rack that extended up to 30 slots. RSLogix 5000 software version 20.00.00

with the 1747-AENTR module version 1.1 supports a maximum chassis size of 13

slots and only one chassis. Logix Designer Application version 21.00.00 or later

with the 1747-AENTR module version 2.1 supports up to 30 modules and up to 3

chassis.

Keeping I/O With the introduction of the 1747-AENTR module, you can potentially lower

the risk, decrease conversion time, and lower the cost of converting an SLC

system to a Logix system. Studio 5000 Logix Designer version 21 and later lets

IMPORTANT

RSLogix 5000 software version 20.00.00 with any version of the 1747-

AENTR module supports a single chassis with up to 13 slots. You must

have Logix Designer Application version 21.00.00 or later and a 1747-

AENTR module version 2.1 or later to support up to 30 modules.

16 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 1 Overview

you keep your existing SLC I/O modules while migrating to a Logix controller.

The existing SLC I/O can be added to the Logix controllers I/O tree by replacing

the SLC controller or SLC adapter with a 1747-AENTR module. No changes are

needed to individual SLC I/O modules, but new EDS files have been developed

for the existing supported modules. These new EDS files are installed with

RSLinx software version 2.59. The EDS files can be verified in RSLinx software

by viewing the modules EDS file. The correct EDS files have a ModDate of 2011;

incorrect files have a ModDate of 1999.

RSLinx software version 2.59 installs new EDS files for all 1746 supported

I/O modules. However, the 1747-AENTR EDS file installed by RSLinx software

version 2.59 is not the latest version. You must update the

1747-AENTR EDS file to the latest version, which is currently version 2.3.

Common symptoms of creating an RSLogix 5000 project with an incorrect

1747-AENTR EDS file include the following:

• Incorrectly getting ‘Module Configuration Rejected fault code 16#0009’

to a properly configured module under the 1747-AENTR module

• Inability to convert an RSLogix 5000 project from one controller type to

another

• Inability to open a valid project on another computer

The corrective actions include uninstalling the incorrect EDS file and updating

to the correct version EDS file, possibly deleting the 1747-AENTR module and

its children from the I/O tree, and exporting and importing the project. If you

are using EDS revisions earlier than 2.3 and you right-click on the 1747-AENTR

module, you do not see a selection for ‘Upload EDS from device’. If you are

using EDS revision 2.3 or later and you right-click the 1747-AENTR module, you

see a selection for ‘Upload EDS from device’.

IMPORTANT

See Appendix B for a list of supported and unsupported I/O modules.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 17

Chapter 2

Migration Considerations

Define Future Requirements As you investigate the prospect of upgrading current control systems to newer

technology, it is important to factor in all aspects of the migration. Deciding

how to phase in the new system can be challenging due to conversion time and

physical considerations. Rockwell Automation has tools to assist with the

conversion of the program code to minimize the engineering design time. But,

what about the physical layout of the new system? Does it make more sense to

leave the existing legacy I/O and wiring in place and save the I/O conversion

for a later date? Or should the entire system be upgraded all at once? How

might the hardware costs for each of these scenarios be affected?

The process for converting your SLC program to a ControlLogix 5580 or 5570

controller is similar to what is presented in this manual.

Device Level Ring Topologies

While the 1747-AENTR adapter can be a member of a ring, the adapter does not

support being an Active Ring Supervisor or a Back-up Supervisor. For more

information on Ethernet network rings and ring supervisors, see the

EtherNet/IP Embedded Switch Technology Application Guide, publication

ENET-AP005

.

Using DeviceNet Network

Existing SLC systems that use 1747-SDN modules must replace the 1747-SDN

module with a different DeviceNet® scanner because the 1747-SDN module is

not supported by the 1747-AENTR module. Depending on the application and

Logix processor that is selected, we recommend a 1756-DNB module, a 1769-

SDN module, or a 1788-EN2DNR module.

The CompactLogix 5380 controller does not have a module that supports

DeviceNet at the time this publication is released. Use the 1788-EN2DN

module to connect the CompactLogix 5380 controller to the DeviceNet devices.

The 1747-SDN module scans I/O and places the data in a combination of I1

Input, O0 Output, M1 Input, and M0 Output files. The 1747-SDN module must

be replaced in the converted system with a different DeviceNet scanner. After

the replacement, the original 1747-SDN module data must be MOVed/COPied

to/from the original I1, O0, M1, and M0 locations to the new Logix tag

locations.

18 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

Use of Advanced Modules

The 1746-HSCE, 1746-QS, 1746-BAS/B, and the 1746-BAS-T modules are

considered advanced modules because they transfer Input data, Output data,

and in an SLC environment M0 and M1 files. In the Logix Designer

application, connections are established to these modules by using an

Exclusive Owner Advanced connection. The Exclusive Owner Advanced

connection enables the transfer of the additional data that is supplied by the

1746 modules M0 and M1 files. Advanced connections transfer Input, Output,

M0, and M1 data from the SLC I/O module via a single connection in the Logix

Designer application. This data in the RSLogix 500 environment was obtained

in the equivalent of two separate transactions.

Advanced modules do require some additional setup and configuration.

Advanced modules also do not have descriptive tag names like most non-

advanced SLC I/O modules. All Advanced modules require additional steps and

programing to migrate.

See Use Advanced Modules in a Logix System

on page 81 for information.

Communication with SLC Controllers Over Serial Networks

Be aware of other networks and take them into account when planning a

conversion. This is a brief overview of networks that can be present in the

existing architecture.

If after the conversion you must keep communication with existing nodes,

various communication modules can facilitate this messaging.

The Compact 5000 I/O serial module provides two independent channels that

function as network interfaces to a wide variety of RS-232C, RS-422, and RS-

485 devices. The module has two channels that are independent of each other.

The channels can transmit data to and receive data from serial devices using

the following communication modes:

• Generic ASCII

IMPORTANT

The exact process of these moves is beyond the scope of this document;

expect this part of the conversion to take additional work and time.

You can also use products from various Rockwell Automation

Encompass™ partners for support on a specific protocol.

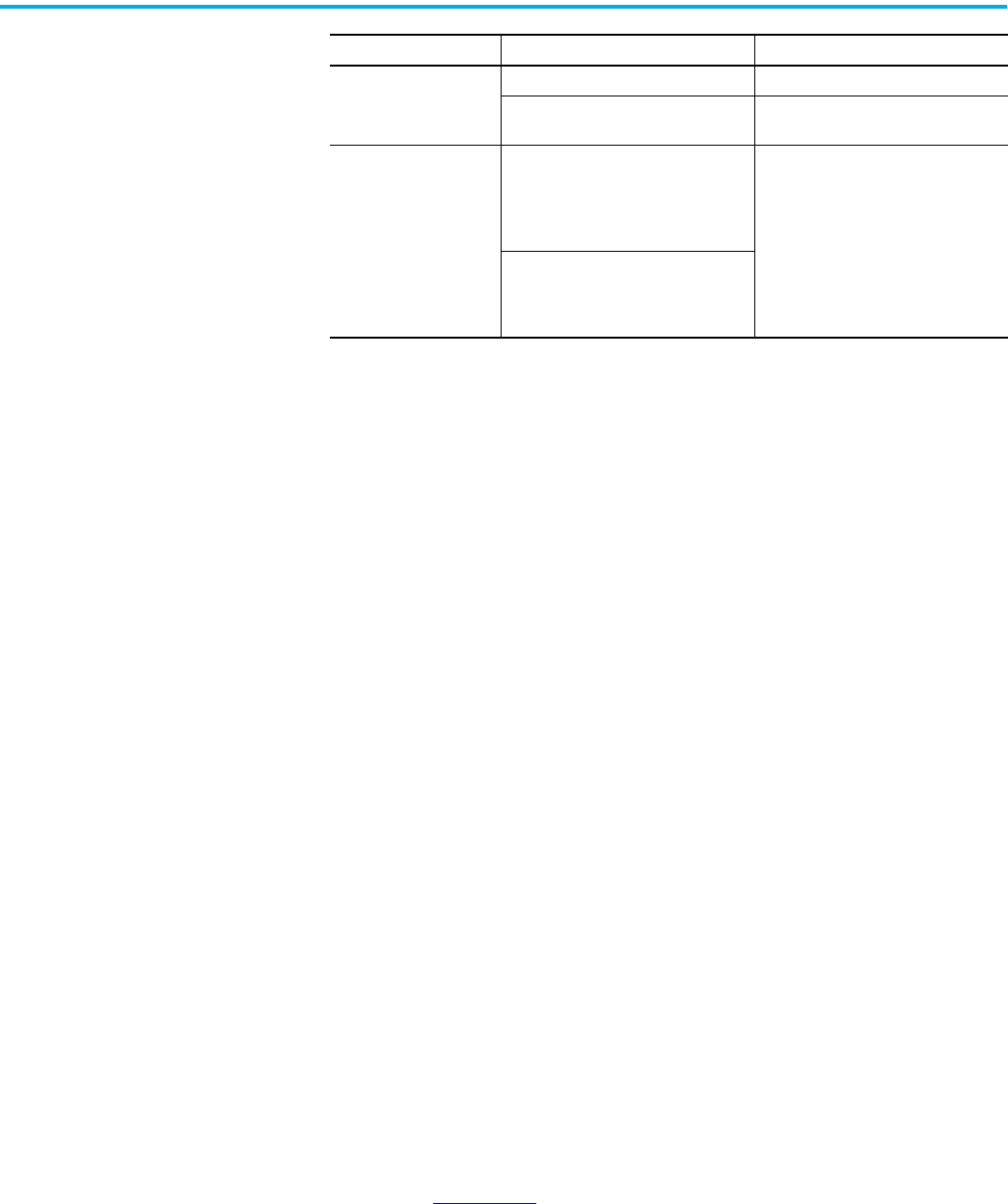

Network Modules See Publication

DH-485 network 1756-DH485 communication module 1756-UM532

DH+™ network 1756-DHRIO communication module 1756-UM514

Ethernet network 1756 Ethernet modules ENET-UM001

Generic ASCII

5069-SERIAL 5069-UM003

Modbus

DH-485 network

DF1 network

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 19

Chapter 2 Migration Considerations

• Modbus RTU (Master/Slave)

• Modbus ASCII (Master/Slave)

The serial module can reside locally in a CompactLogix 5380 or Compact

GuardLogix® 5380 system. The module can also reside in a remote Compact

5000 I/O system accessible using an EtherNet/IP network.

For more information on how Compact 5000 I/O serial modules function in a

control system, see the Compact 5000 I/O Serial Module User Manual,

publication 5069-UM003

.

Power Considerations The SLC 500 controllers require an SLC power supply module on the leftmost

slot to provide power to all modules on the chassis. This powers up the

controller and the I/O modules. This also facilitates communication through

the backplane.

The CompactLogix 5380 controllers require a 24V DC source supply that is

connected to the MOD power terminal to provide power to all modules. Unlike

SLC 500 controllers, CompactLogix 5380 controllers do not require a chassis.

For detailed power considerations for controllers, sensor, actuator, and

backplane, see the SLC 500 Hardware Migration Reference Manual,

publication 1746-RM003

.

Using Integrated

Architecture Builder to Plan

Hardware Migration

Once you have planned your overall migration approach, let Integrated

Architecture Builder (IAB) help plan the details. The SLC migration wizard

embedded in IAB steps you through the system configuration process, letting

you make the decisions on which components you prefer to keep and reuse

and which components you prefer to replace. If you choose to reuse the

SLC I/O modules, IAB verifies module support and power supply loading and

helps you lay out the new EtherNet/IP network.

This section uses the SLC Migration Wizard within IAB to assist with the

conversion of the existing SLC hardware to a CompactLogix system. The

process for converting your SLC program to ControlLogix 5580 or 5570

controller is similar to what is presented in this manual.

Replace Only the Local SLC Controller

1. Go to Start > Programs > Rockwell Automation > Integrated Architecture

Builder > Integrated Architecture Builder

or double-click the Integrated Architecture Builder icon on the computer

desktop to launch IAB.

The IAB opening dialog box appears.

2. Click New Project.

20 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

3. In the Workspace Name text box, type an appropriate name, such as ‘SLC

Migration Wizard’, and click OK.

4.

Under Wizard View, click SLC Migration.

Clicking the wizards that are listed under Available Assistants provides

an overview of the wizard.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 21

Chapter 2 Migration Considerations

5. In the SLC Migration Chassis Selection dialog box, click Add Chassis.

IAB opens the Add Chassis dialog box.

6. Click OK to accept the default name (SLC001) for the new chassis.

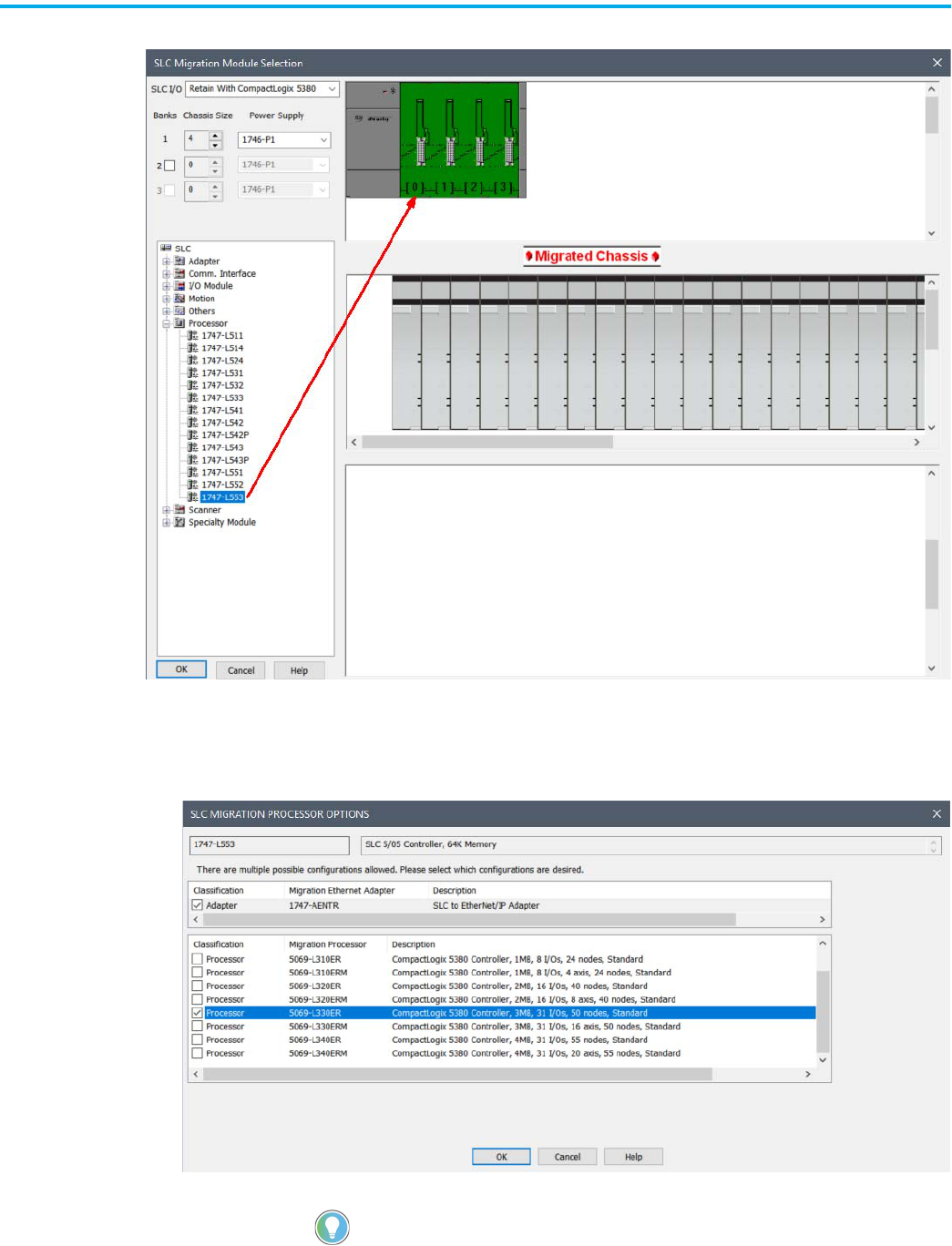

IAB opens the SLC Migration Module Selec

tion dialog box.

This is where

you make the conversion

selections for this chassis. Notice the diff

erent

a

reas of this window.

Click for more information

about the wizard.

22 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

7. Select your chassis size and choose power supply.

8. From the Processor module list, expand the Processor heading and drag

your processor module to slot 0 of the SLC chassis.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 23

Chapter 2 Migration Considerations

Because IAB has found multiple possible CompactLogix controller

migration options, the ‘SLC Migration Conflict Resolution Dialog’

box appears.

24 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

9. Select a processor from the list and click OK.

In this example, we show the CompactLogix 5380 5069-L330ER

controller.

IAB adds processors to both the SLC chassis and the replacement

CompactLogix 5380 chassis. Additionally, IAB also adds a 1747-AENTR

Ethernet adapter to the retained I/O on the SLC chassis at the bottom of

the display.

10. Repeat steps 8 and 9 to fill remaining slots.

Most SLC I/O discrete, analog, and specialty modules are compatible

with the 1747-AENTR adapter.

For a list of supported and unsupported modules, see I/O Modules

on

page 75.

Conflict resolution dialogs appear when you must make a decision about

the conversion. The information in the dialog box is specific to the action

you are performing. In this case, we must select the CompactLogix

processor that we wish to use.

If you incorrectly place a module, simply right-click the module and click

Remove Module to try again.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 25

Chapter 2 Migration Considerations

If you have a module that is not compatible, the following warning

occurs.

11. Once the local SLC chassis is complete, click OK.

12. In the SLC Migration Chassis Selection dialog box, click Generate

Hardware to create the wizard-defined CompactLogix configuration

in IAB.

13. Click the Hardware tab in the lower left corner of the IAB window.

14. Click the SLC_Migration.1_SLC001 chassis to see the hardware.

IMPORTANT

Modules not supported as part of a retained I/O solution, when

connected to a Logix controller, are not placed into the lower chassis in

IAB.

26 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

This chassis contains all SLC I/O from the local rack that we replaced. A

1747-AENTR module has been added to connect this I/O remotely over

Ethernet to the CompactLogix controller that is replacing our SLC

processor.

15. Click the save icon to save your project.

Replace the Local SLC System with CompactLogix System

Although retaining the SLC I/O when converting to a Logix system can save on

rewiring costs, adding a controller and a power supply to an existing control

panel can prove to be impossible due to physical space limitations. In such

optional cases, SLC conversion solution can actually involve converting the I/O

to the Compact I/O or POINT I/O™ platforms in addition to converting to a

Logix controller.

1. Go to Start > Programs > Rockwell Automation > Integrated Architecture

Builder > Integrated Architecture Builder

or double-click the Integrated Architecture Builder icon on the computer

desktop to launch IAB.

The IAB opening dialog box appears.

2. Click New Project.

The Create New Workspace dialog box appears.

Hardware Tab

SLC_Migration.1_SLC001

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 27

Chapter 2 Migration Considerations

3. In the Workspace Name text box, type an appropriate name, such as ‘SLC

Migration Wizard’, and click OK.

4. Click SLC Migration in the Wizard View.

Click Available Assistants for more information about each assistant.

28 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

5. In the SLC Migration Chassis Selection dialog box, click Add Chassis.

IAB opens the Add Chassis dialog box.

6. Click OK in the Add Chassis dialog box to accept the default name for the

new chassis (SLC001).

IAB opens the SLC Migration Module Selection dialog box. This is where

you make the conversion selections for this chassis. Notice the different

areas of this window.

7. Select your chassis size and choose power supply.

8. From the Processor module list, expand the Processor heading and drag

your processor module to slot 0 of the SLC chassis.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 29

Chapter 2 Migration Considerations

Because IAB has found multiple possible CompactLogix controller

migration options, the SLC Migration Conflict Resolution Dialog

box appears.

Conflict resolution dialog boxes appear when you must make a decision

about the conversion. The information in the dialog box is specific to the

action you are performing. In this case, we must select the

CompactLogix processor that we wish to use.

30 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

9. Select a processor in the list and click OK.

In this example, we show the 5069-L330ER module.

IAB adds processors to both the SLC chassis and the replacement

CompactLogix chassis. Additionally, IAB also adds a 1747-AENTR

Ethernet adapter to the retained I/O on the SLC chassis at the bottom of

the display.

10. Repeat steps 8 and 9 to fill remaining slots.

Most SLC I/O discrete, analog, and specialty modules are compatible

with the 1747-AENTR adapter.

For a list of supported and unsupported modules, see I/O Modules

on

page 75.

If you have a module that is not compatible, the following warning

occurs.

If you incorrectly place a module, right-click the module and click

Remove Module to try again.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 31

Chapter 2 Migration Considerations

11. Once the local SLC chassis is complete, click OK.

12. In the SLC Migration Chassis Selection dialog box, click Generate

Hardware to create the wizard-defined CompactLogix configuration in

IAB.

13. Click the Hardware tab in the lower left corner of the IAB window

and click the chassis to see the hardware.

This chassis contains all SLC I/O from the local rack that was replaced.

14. Click the save icon to save your project.

IMPORTANT

Modules not supported as part of a retained I/O solution, when connected

to a Logix controller, are not placed into the lower chassis in IAB.

Hardware Tab

Click your chassis

32 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

Adding a Chassis

If your system does contain additional remote chassis, you can add to the

existing chassis.

1. On the SLC Migration Chassis Selection dialog box, click Add Chassis.

This chassis replaces the remote SLC I/O chassis in your existing system.

2. Name this chassis, for example, SLC002_Remote, and click OK.

3. Select the chassis and power supply.

4. Choose to retain the SLC I/O for this chassis.

5. Add your remote I/O adapter to slot 0 of the SLC chassis.

Chassis Size

Power Supply

Add Modules

IMPORTANT

IAB replaces the 1747-ASB adapter with a 1747-AENTR Ethernet adapter in

the replacement SLC remote I/O chassis.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 33

Chapter 2 Migration Considerations

6. Add in the rest of your I/O modules.

Most 1746 and 1747 discrete, analog, and specialty modules are

compatible with the 1747-AENTR adapter.

For a list of supported and unsupported modules, see I/O Modules

on

page 75.

If you have a module that is not compatible, the following warning

occurs.

7. Once the remote SLC chassis is complete, click OK.

8. In the SLC Migration Chassis Selection dialog box, click Generate

Hardware to create the wizard-defined CompactLogix configuration in

IAB.

9. Click the Hardware tab in the lower left corner of the IAB window.

10. Click the SLC_Migration.1_SLC002 - Remote chassis to see the hardware.

This chassis contains all SLC I/O from the remote rack that you replaced.

A 1747-AENTR module has been added to connect this I/O remotely over

Ethernet to the CompactLogix controller that is replacing our SLC

processor.

11. Click the save icon to save your project.

You have three options when converting the second, remote chassis:

• To convert the local SLC I/O, leave the remote SLC chassis in place, add

the Ethernet wiring, and rebuild the BOM.

If you incorrectly place a module, simply right-click the module and click

Remove Module to try again.

IMPORTANT

Modules not supported as part of a retained I/O solution, when

connected to a Logix controller, are not placed into the lower chassis

in IAB.

34 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

• Add the I/O modules from the second SLC chassis to the new local

CompactLogix system.

• Swap out the remote SLC I/O chassis with a more cost-effective FLEX™

I/O or POINT I/O system.

In either case, this is best done outside the wizard.

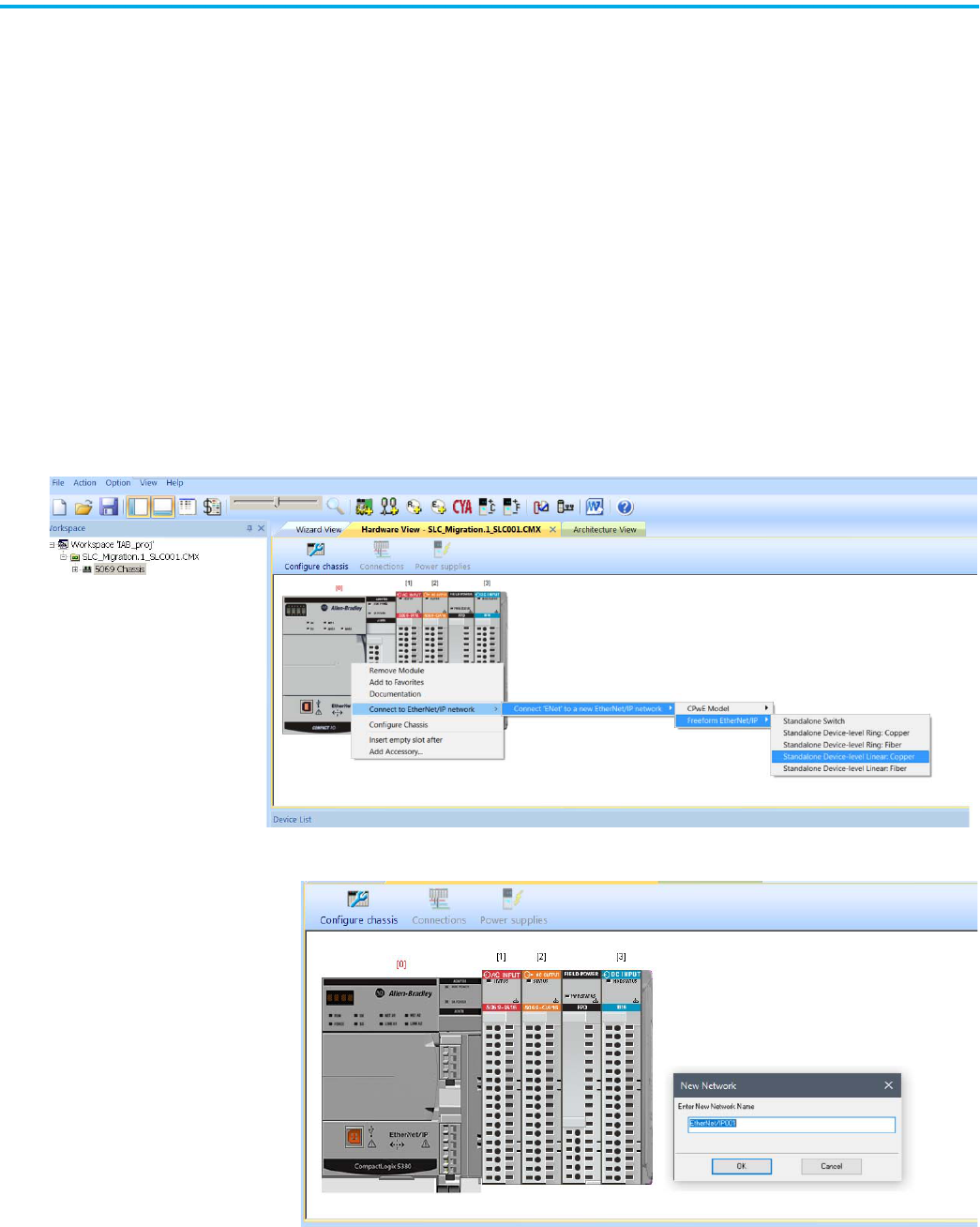

Network Connection Options for the Remote (SLC System) I/O Chassis

Connecting I/O systems to a controller is best accomplished by first creating a

network connection on the controller itself. Because the remote SLC I/O

chassis is configured with a 1747-AENTR Ethernet adapter, you can connect it

to the CompactLogix chassis by using an Ethernet network.

1. In the Hardware View for the SLC_Migration_SLC001.CMX chassis,

right-click the controller and choose Connect to EtherNet/IP network >

Connect 'Enet' to new EtherNet/IP network > Freeform EtherNet/IP >

Standalone Device-Level Linear: Copper.

2.

3. Click OK to accept the default network name.

4. Choose the Network tab.

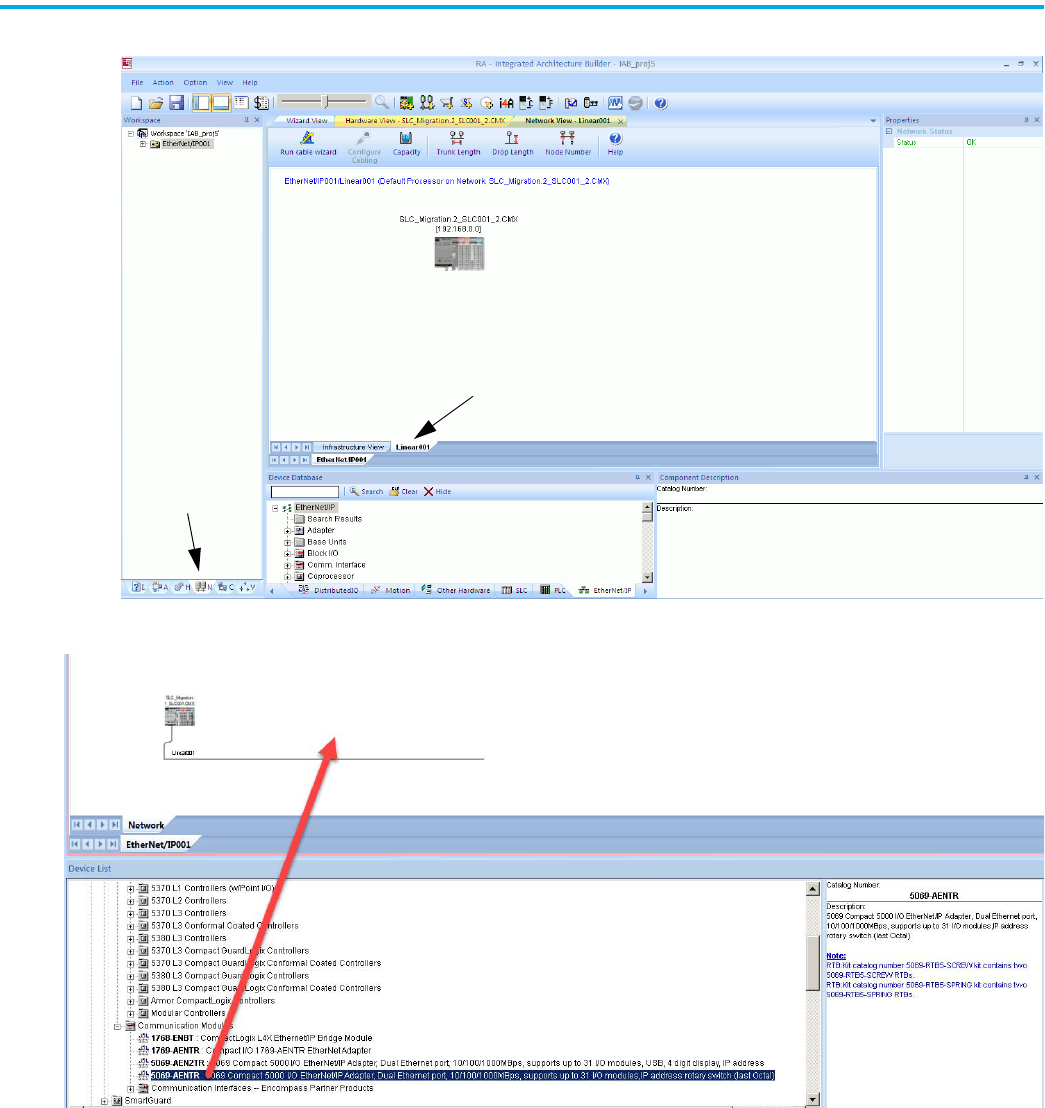

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 35

Chapter 2 Migration Considerations

5. Drag-and-drop a remote I/O adapter into the network space.

In this example, we use the Compact 5000 I/O 5069-AENTR adapter.

Network View

Linear001 Tab

36 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

6. Add an I/O module to the remote I/O adapter.

In this example, we add an 8-point analog input terminal.

7. The example SLC architecture is complete. You can now save your

project.

Create Project Bill of Materials

Follow these steps to get an idea of how much your conversion is going to cost

and what is needed.

1. From the Menu Bar, click the Project Bill of Materials (BOM) icon.

From this dialog box, we can get a clear view of the material necessary to

make the conversion based on the chassis layouts.

Project BOM

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 37

Chapter 2 Migration Considerations

In addition, the radio buttons along the bottom of the dialog box let you

manipulate the information either as a consolidated spreadsheet or by

slot location. All of these arrangements incorporate pricing either with

List or Custom pricing models.

2. Click Close to close the BOM window.

38 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 2 Migration Considerations

Notes:

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 39

Chapter 3

Conversion of Programs

Introduction You can use RSLogix 500 version 12 to convert a .RSS program into .ACD

program. This means that you can migrate an SLC 500 project into a Studio

5000 project with its in-built migration capability.

This section will step through the program migration with RSLogix 500

version 12 for an SLC 500 controller.

For hardware migration, see the Logix 5000 Controllers General Instructions

Reference Manual, publication 1756-RM003

.

For a more detailed explanation of the Project Migrator, see SLC 500 Hardware

Migration Reference Manual, publication 1746-RM003

.

Download the Standalone RSLogix 500

You can download a standalone copy of the RSLogix™ Project Migrator from

the Rockwell Automation Compatibility & Download page

.

The Studio 5000 environment, which includes the Logix Designer

application, was introduced in version 21. If you are using RSLogix 5000

software version 20, the steps are nearly identical.

IMPORTANT

The process for converting an SLC system to a ControlLogix system is

similar to converting to a CompactLogix system.

40 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 3 Conversion of Programs

1. Go to Rockwell Automation Compatibility & Download page.

2. Under the Download section, click ‘Find Downloads’.

3.In the Product Search box of the page appears, type RSLogix 500.

4. From the product list, select RSLogix 500 > version 12.

5. From the selected versions on the right side of the screen, click

RSLogix 500 version 12 and click Downloads.

6. On the Downloads page, click the show downloads icon.

IMPORTANT

You must log in with your Rockwell Automation account to be able to

download the software.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 41

Chapter 3 Conversion of Programs

The RSLOGIX 500 dialog box appears with the links of all files that you

can download for version 12.

7. Under the General options, click ‘Download Software’.

What to Expect from the RSLogix Project Migrator

The goal of the RSLogix Project Migrator is to reduce the amount of work

involved in migrating a PLC-5 or SLC 500 program to a Logix project. The

RSLogix Project Migrator automatically converts the program logic, but it is

not the complete solution. Depending on the application, you may need to do

additional work to make the converted logic work properly.

The RSLogix Project Migrator produces a syntactically correct import/export

file, but the exact intent of the original application could be lost. This loss could

be due to differences in rules. (For example, rules of precedence, rules of

indexed addressing, or rules of I/O addressing). When there is an error in the

translation, the RSLogix Project Migrator records the error in the rung of the

Logix routine in which it occurred. You can use that error message to analyze

and fix the error.

Application Code

Conversion

The first step in a procedure of this type is to export the current SLC project

into an ASCII text format.

1. From the desktop, double-click the RSLogix 500 programming software icon.

Or, choose Start > All Programs > Rockwell Software > RSLogix 500 >

RSLogix 500.

2. From the File menu, choose Open to open the file you want to convert.

The first step is to export the current SLC project into an ASCII text

format.

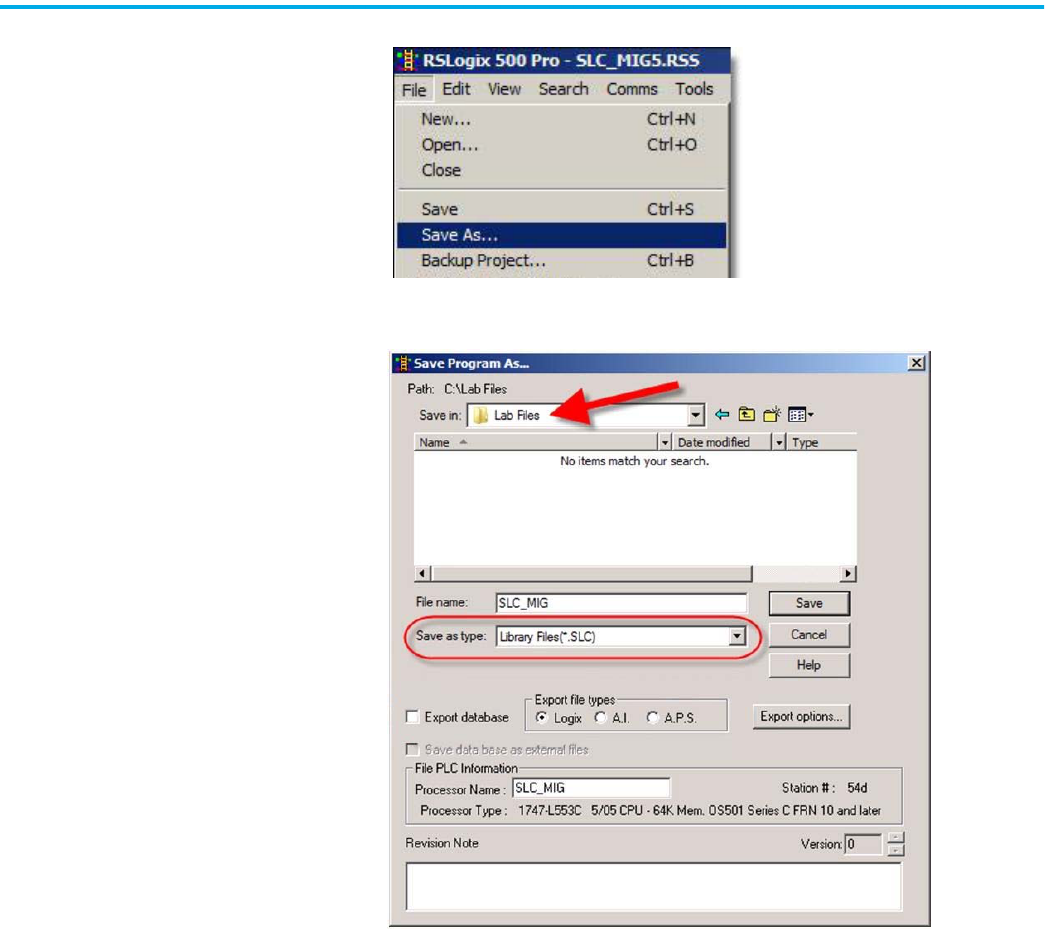

3. From the File menu, choose Save As.

ATTENTION: After running the conversion process, the resulting import/export file

still requires further manipulation. You must map the I/O and use BTD, MOV, or CPS

instructions to place this mapped data into the structures created by the

conversion process.

42 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 3 Conversion of Programs

4. Browse to the folder where you are saving the converted program.

5. Set the file type to ‘.SLC.

The RSLogix Project Migrator accepts projects that have been saved as

.SLC file type.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 43

Chapter 3 Conversion of Programs

6. Click Save to continue.

Additional file export options are presented. For this example, we want

to export the entire project, so the default settings here are fine.

7. Click OK.

After the file is converted, select the export options.

From the Tools menu, select Database >ASCII Export.

The Document Database ASCII Export window displays.

8. From the CSV tab, select Export Addr/Symbol Desc. and Instruction

Comments, and then click OK.

44 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 3 Conversion of Programs

The Select Export Destination Directory dialog displays.

9. Browse to the folder where you saved the .slc file, and click OK.

The Export Result dialog displays.

10. Click OK to close the RSLogix 500 software.

Convert RSLogix 500

Projects Into Studio 5000

Projects

Before you start the migration process, delete or remove unused memories,

addresses, and routines:

• Delete unused memory from Tools > Delete Unused Memory.

• Delete unused addresses from Tools > Database > Delete

Unused Addresses.

• Remove SFC and STX routines to help avoid syntax errors that RSLogix

Project Migrator fails to convert if encountered in the PC5 file.

1. From the RSLogix 500 version 12 software, open the SLC 500 project that

you want to convert.

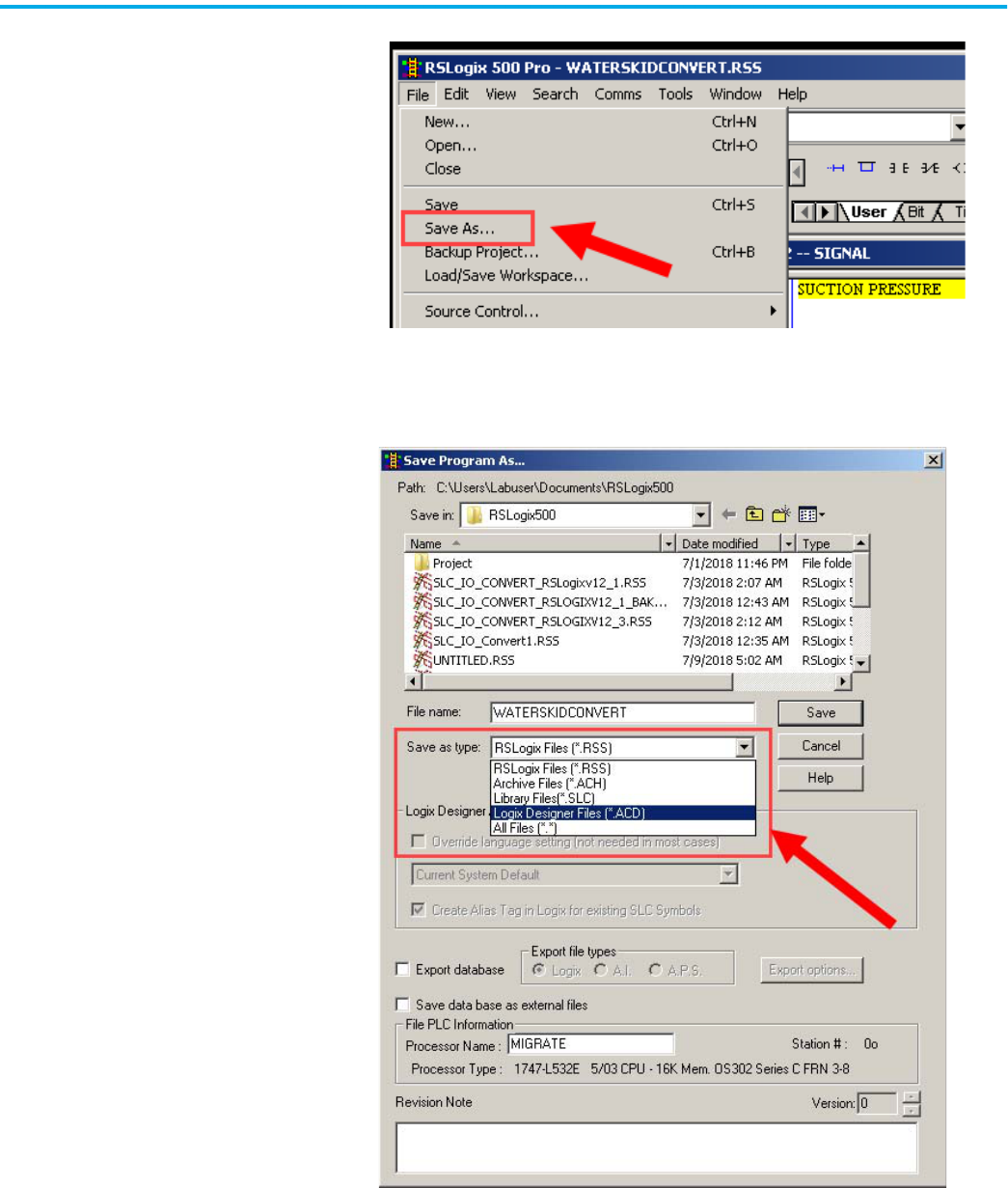

2. Click File > Save as…

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 45

Chapter 3 Conversion of Programs

The Save Program As… dialog box appears.

3. From the 'Save as type' pull-down menu, select Logix Designer

application Files (*.ACD) and click Save.

The Logix Designer application Export dialog box appears.

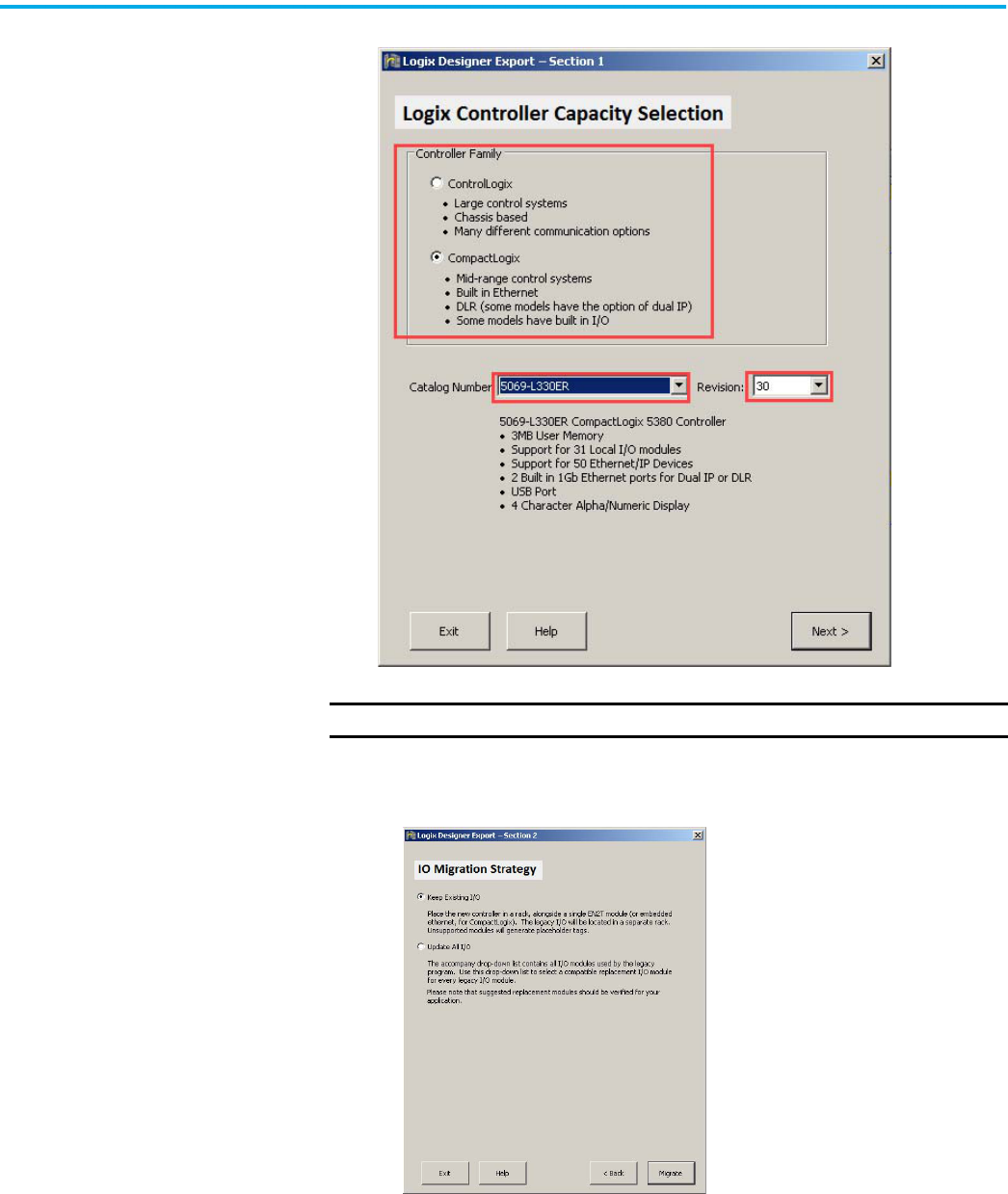

4. Select from the following options and click Next.

• Controller Family that you are migrating to

• Catalog Number

• Revision Number

46 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 3 Conversion of Programs

5. Select your I/O Migration Strategy.

a. Select 'Keep Existing I/O' to indicate that you are using a 1747-AENTR

with the existing SLC I/O modules from your system.

.

b. Select 'Update All I/O' to allow the tool to select a compatible module. In

this example, we place the new I/O module in a remote rack.

IMPORTANT

This tool supports direct conversion to revision 30 or later.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 47

Chapter 3 Conversion of Programs

6. Click Migrate.

The 'Logix Designer Export - Progress ' dialog box shows the progress of

the migration process.

When the migration process is complete, open the migrated project in

Studio 5000.

Resolve the Differences in

the New Logix Program

Now that the SLC 500 program has been initially converted to a Logix

program, you need to look at some of the most common elements that must be

addressed for the CompactLogix project to properly control the installed

SLC I/O modules.

The migration tool supports CompactLogix version 30 or later. Ensure

that Studio 5000 is pre-installed with the revision of CompactLogix

equal to what you specified in step 4

.

48 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 3 Conversion of Programs

SLC Controllers Data Tables and Logix Controller Tags

The SLC 500 processors store all data in global data tables. You access this data

by specifying the address of the data you want. A Logix controller supports

data that is local to a program and data that is global to all tasks within the

controller. A Logix controller can also share data with other controllers, and

instead of addresses, you use tags to access the data you want. Each SLC 500

data table file can store several words of related data. A Logix controller uses

arrays to store related data. The RSLogix Project Migrator converts the

SLC 500 data table files into Logix arrays.

With a Logix controller, you use a tag (alphanumeric name) to address data

(variables). The controller uses the tag name internally and does not need to

cross-reference a physical address.

• In conventional programmable controllers, a physical address identifies

each item of data.

- Addresses follow a fixed, numeric format that depends on the type of

data, such as N7:8, F8:3.

- Symbols are required to make logic easier to interpret.

• In Logix controllers, there is no fixed, numeric format. The tag name

itself identifies the data.

- Organize your data to mirror your machinery.

- Document (through tag names) your application as you develop it.

Resolve Program Code Issues

The RSLogix Project Migrator inserts a Program Conversion Error (PCE)

instruction within the appropriate ladder rung to help you identify possible

errors with the conversion. To complete the conversion process, locate,

analyze, and fix any discrepancies involving the PCE instructions.

Work with PCE Instructions

The RSLogix Project Migrator inserts a PCE instruction within the appropriate

ladder rung to help you identify possible errors with the conversion. To

complete the conversion process, locate, analyze, and fix any discrepancies

using the PCE instructions.

For a list of PCE instruction errors, see Appendix A

Program Conversion

Errors (PCE) Messages on page 73

.

See Appendix B for supported and unsupported I/O modules.

For a complete list of the PCE instruction Message IDs and their

descriptions, please refer to Appendix A

.

IMPORTANT

After the correction of any errors, you must still spend time running

and debugging the machine or process.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 49

Chapter 3 Conversion of Programs

Locate PCE Instructions

You can locate all PCE instructions by verifying the logic. The

Verify > Controller task compiles the Logix program and checks for errors.

This is an easy way to see where all of the PCE instructions are because the

error checking points them out. To locate the PCE instructions, follow

these steps.

1. From the Logic menu, select Verify > Controller.

Or, from the menu bar, click the Verify Routine icon.

The bottom of the dialog box displays results.

2. Double-click the error shown in the error window to go directly to the

rung where the error occurred.

Recognize Instructions

Text is appended to the rung comments that have the PCE instruction. The

message text begins with asterisks(*) and the words “Generated by RSLogix

Project Migrator”, and ends with asterisks.

An example of a PCE instruction follows:

*** Generated by RSLogix Project Migrator: Source and destination types may

differ *** ";

N: PCE(120, PCE011) COP(I1_008, N23[0], 4);

Some Warnings reference bits that are used as outputs in more than one

rung, Duplicate Destructive Bits. While using this type of coding is not

recommended, with careful programming, using the same outputs on

several different rungs can be done.

50 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 3 Conversion of Programs

Resolve PCE Instructions

Once you import the converted Logix project, find each PCE instruction. A PCE

instruction highlights a possible conversion error. Delete each PCE instruction

and replace it with the appropriate, corrected logic.

Work with UNK Instructions

The RSLogix Project Migrator converts some PLC-5 and SLC 500 instructions

that have no equivalent in the Logix architecture. Once you import these

instructions into the Logix project, they appear as UNK instructions. You must

delete each UNK instruction and replace it with the appropriate corrected

logic.

Common PCE Issues Translation greatly reduces the amount of work in a conversion; however, you

may still get conversion errors that must be addressed individually.

• A common error occurs with all Timer related instructions. The timer

instruction and its associated elements are compatible between the SLC

500 controller and the Logix platform. However, the SLC 500 controller

supports only a .01 or 1 second time base for timers. Logix controllers

support a 1 ms time base. The code conversion resulted in an increase of

the timer Preset value by an order of magnitude. That is, the original

Preset in the SLC 500 controller for this timer was 32767 and now it has

been changed to 327670. All related references to this timer have been

adjusted automatically, except those that reference a specific bit within

the Accum or Preset itself. This can lead to errors on any rung that

addresses a Timer.PRE or Timer.ACC because the scaling can be off and

can be corrected only by user intervention.

• Another common conversion tool error is related to MSG instructions.

Not all SLC 500 MSG instructions convert completely and, after the

conversion, you need to verify that the data and path in all MSG

instructions are correct.

• Several other SLC instructions may not convert properly or may not have

the intended behavior. Among the more significant SLC instructions that

can have issues are serial port instructions, Block Transfer instructions,

FBC, and PID.

Map PLC/SLC Messages If your application does not require you to communicate with a legacy

controller, you can skip this section.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 51

Chapter 3 Conversion of Programs

Map PLC/SLC Messages is a built-in feature of Logix controllers that lets older

products that support a data table memory architecture, like PLC-2®, PLC-5,

and SLC controllers, read/write to a Logix controller that has a tag-based

memory architecture.

If after the conversion, legacy SLC controllers need to communicate to the

converted Logix controller, Map PLC/SLC Messages can facilitate this. See the

example below for an overview explaining PLC/SLC Mapping.

Map I/Os The file structure in a Logix controller is tag-based. To facilitate the

conversion, the RSLogix Project Migrator creates tags and arrays of tags to

align and map the PLC-5 or SLC 500 files. See the following table for some

examples:

EXAMPLE

If an incoming message from an SLC controller requests to read data

from file N7:x, the Logix controller replies with data from tag

SLC_Reads_This_LogixTag[x].

If an incoming message from an SLC controller requests to write data to

file N10:x, the Logix controller places that data in tag

SLC_Writes_to_This_LogixTag[x].

SLC 500 Address Map to the Logix Address

N7:500 N7[500]

N17:25 N17[25]

R6:100 R6[100]

C5:0 C5[0]

T4:6 T4[6]

52 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 3 Conversion of Programs

By default, the I/O data in CompactLogix 5380 controller is grouped by

“channel”, and is no longer shown at the word level. For example, 'I:2/3' is a

word-level digital input data. In the CompactLogix 5380 controller, the same

data is accessible by 'Local: 2:I.Pt03.Data'. This data is grouped under 'Local:

2:I.Pt03', along with 'Fault' and 'Uncertain' statuses for you to verify the data.

In case there is no direct replacement for the I/O module, the migration

wizard allows you to create an array variable placeholder and maintain all your

existing assignment in your original program.

Resolve Issues with

Physical I/Os

When your migration strategy is to 'Keep Existing I/O', the SLC I/O is

considered remote. Each SLC chassis is connected through the 1747-AENTR

Ethernet adapters. This eliminates quite a bit of extra code that is otherwise

required to communicate to the remote I/O.

There are three options to resolve physical I/O issues:

• MOV instructions

• CPS instructions

• Aliasing instructions

Each has its advantages and drawbacks depending on the type of data. Ideally,

the RSLogix Project Migrator identifies I/O to be converted and offers you

options during the conversion process rather than leaving this to you

afterwards.

These examples illustrate situations that you can encounter when translating

your files.

I:1.0

Local IO: Local:1.I.Ch00.Data

Remote IO: [AdapterName]: 1.I.Ch00.Data

I:2/3

Local IO: Local: 2:I.Pt03.Data

Remote IO: [AdapterName]:2:I.Pt03.Data

O:3.0

Local IO: Local:3:O.Ch00.Data

Remote IO: [AdapterName]: 3:O.Ch00.Data

O:4/7

Local IO: Local:4:O.Pt07.Data

Remote IO: [AdapterName] :4:O.Pt07.Data

EXAMPLE

Here is an example of placeholder tag for 1746-NI4:

Existing input assignment will be replaced by the element of the array.

SLC 500 Address Map to the Logix Address

Input module data group for CompactLogix 5380 controller.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 53

Chapter 3 Conversion of Programs

MOV Example

This first rung is used to initialize the configuration for a 1746-NT4 module in

slot 5 of the local SLC 500 chassis.

The memory structure in the new environment is not the same as RSLogix 500.

As a result, the Dest data location is not an array variable. We need to replace

the COP instruction with MOV instruction to move the configuration for the

channel to the corresponding module config tag.

This resolves the issue for Channel 0. Additional MOV instructions are

required if other channels are used.

CPS Example

In RSLogix 500 software in order for many specialty modules to transfer data

over RIO, sophisticated instructions called Block Transfers were used. In the

IMPORTANT

The configuration for the individual channel resides in the C word of the

module. These words are separated and a COP instruction cannot copy

all configuration into the respective C word. The simplest way is to use

MOV instruction 4 times to move each configuration data into the

respective channel configuration.

54 Rockwell Automation Publication 5069-AP001A-EN-P - August 2020

Chapter 3 Conversion of Programs

Logix Designer application, these Block Transfers were replaced with the MSG

instructions shown below.

The need for messaging to/from these modules is no longer needed because

the controller is communicating with them directly through the 1747-AENTR

module.

Original RSLogix 500 Software Block Transfer Instructions

• Data to be written to the remote module in our example, was entered

into N11:0 (2 words).

• Data to be read from the remote module into the controller was placed

into N13:0 (2 words).

If consecutive I/O groups map to consecutive elements in an array, a CPS

instruction must be used. Use a CPS instruction when you copy I/O or

Produced/Consumed peer data of more than one DINT. This is the only

information you need to create the instructions necessary to replicate the

original program functionality.

You can delete the rungs containing the PCE and MSG instructions and replace them

with CPS rungs.

IMPORTANT

Extensive use of the CPS instruction can lock the tag database, which

could affect other processes.

Rockwell Automation Publication 5069-AP001A-EN-P - August 2020 55

Chapter 3 Conversion of Programs

Alias Example

The rung in this routine uses a timer accumulator to simulate an analog output