i

Writing a Simple Operating System —

from Scratch

by

Nick Blundell

School of Computer Science, University of Birmingham,

UK

Draft: December 2, 2010

Copyright

c

2009–2010 Nick Blundell

Contents

Contents ii

1 Introduction 1

2 Computer Architecture and the Boot Process 3

2.1 The Boot Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2 BIOS, Boot Blocks, and the Magic Number . . . . . . . . . . . . . . . . 4

2.3 CPU Emulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.3.1 Bochs: A x86 CPU Emulator . . . . . . . . . . . . . . . . . . . 6

2.3.2 QEmu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.4 The Usefulness of Hexadecimal Notation . . . . . . . . . . . . . . . . . . 6

3 Boot Sector Programming (in 16-bit Real Mode) 8

3.1 Boot Sector Re-visited . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.2 16-bit Real Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.3 Erm, Hello? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.3.1 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.3.2 CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.3.3 Putting it all Together . . . . . . . . . . . . . . . . . . . . . . . 11

3.4 Hello, World! . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.4.1 Memory, Addresses, and Labels . . . . . . . . . . . . . . . . . . 13

3.4.2 ’X’ Marks the Spot . . . . . . . . . . . . . . . . . . . . . . . . . 13

Question 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.4.3 Defining Strings . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.4.4 Using the Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Question 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.4.5 Control Structures . . . . . . . . . . . . . . . . . . . . . . . . . 17

Question 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.4.6 Calling Functions . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.4.7 Include Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.4.8 Putting it all Together . . . . . . . . . . . . . . . . . . . . . . . 21

Question 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.4.9 Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

ii

CONTENTS iii

3.5 Nurse, Fetch me my Steth-o-scope . . . . . . . . . . . . . . . . . . . . . 22

3.5.1 Question 5 (Advanced) . . . . . . . . . . . . . . . . . . . . . . . 23

3.6 Reading the Disk . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.6.1 Extended Memory Access Using Segments . . . . . . . . . . . . 23

3.6.2 How Disk Drives Work . . . . . . . . . . . . . . . . . . . . . . . 24

3.6.3 Using BIOS to Read the Disk . . . . . . . . . . . . . . . . . . . 27

3.6.4 Putting it all Together . . . . . . . . . . . . . . . . . . . . . . . 28

4 Entering 32-bit Protected Mode 30

4.1 Adapting to Life Without BIOS . . . . . . . . . . . . . . . . . . . . . . . 31

4.2 Understanding the Global Descriptor Table . . . . . . . . . . . . . . . . 32

4.3 Defining the GDT in Assembly . . . . . . . . . . . . . . . . . . . . . . . 35

4.4 Making the Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4.5 Putting it all Together . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5 Writing, Building, and Loading Your Kernel 41

5.1 Understanding C Compilation . . . . . . . . . . . . . . . . . . . . . . . . 41

5.1.1 Generating Raw Machine Code . . . . . . . . . . . . . . . . . . 41

5.1.2 Local Variables . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

5.1.3 Calling Functions . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.1.4 Pointers, Addresses, and Data . . . . . . . . . . . . . . . . . . . 47

5.2 Executing our Kernel Code . . . . . . . . . . . . . . . . . . . . . . . . . 49

5.2.1 Writing our Kernel . . . . . . . . . . . . . . . . . . . . . . . . . 50

5.2.2 Creating a Boot Sector to Bootstrap our Kernel . . . . . . . . . 50

5.2.3 Finding Our Way into the Kernel . . . . . . . . . . . . . . . . . 53

5.3 Automating Builds with Make . . . . . . . . . . . . . . . . . . . . . . . . 54

5.3.1 Organising Our Operating System’s Code Base . . . . . . . . . 57

5.4 C Primer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.4.1 The Pre-processor and Directives . . . . . . . . . . . . . . . . . 59

5.4.2 Function Declarations and Header Files . . . . . . . . . . . . . . 60

6 Developing Essential Device Drivers and a Filesystem 62

6.1 Hardware Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.1.1 I/O Buses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.1.2 I/O Programming . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.1.3 Direct Memory Access . . . . . . . . . . . . . . . . . . . . . . . 65

6.2 Screen Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

6.2.1 Understanding the Display Device . . . . . . . . . . . . . . . . . 65

6.2.2 Basic Screen Driver Implementation . . . . . . . . . . . . . . . . 65

6.2.3 Scrolling the Screen . . . . . . . . . . . . . . . . . . . . . . . . . 69

6.3 Handling Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.4 Keyboard Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.5 Hard-disk Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.6 File System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

7 Implementing Processes 71

7.1 Single Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

7.2 Multi-processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Chapter 1

Introduction

We’ve all used an operating system (OS) before (e.g. Windows XP, Linux, etc.), and

perhaps we have even written some programs to run on one; but what is an OS actually

there for? how much of what I see when I use a computer is done by hardware and how

much is done by software? and how does the computer actually work?

The late Prof. Doug Shepherd, a lively teacher of mine at Lancaster University,

once reminded me amid my grumbling about some annoying programming problem that,

back in the day, before he could even begin to attempt any research, he had to write

his own operating system, from scratch. So it seems that, today, we take a lot for

granted about how these wonderful machines actually work underneith all those layers

of software that commonly come bundled with them and which are required for their

day-to-day usefulness.

Here, concentrating on the widely used x86 architecture CPU, we will strip bare our

computer of all software and follow in Doug’s early footsteps, learning along the way

about:

• How a computer boots

• How to write low-level programs in the barren landscape where no operating

system yet exists

• How to configure the CPU so that we can begin to use its extended functionality

• How to bootstrap code written in a higher-level language, so that we can really

start to make some progress towards our own operating system

• How to create some fundamental operating system services, such as device drivers,

file systems, multi-tasking processing.

Note that, in terms of practical operating system functionality, this guide does not

aim to be extensive, but instead aims to pool together snippets of information from

many sources into a self-contained and coherent document, that will give you a hands-on

experience of low-level programming, how operating systems are written, and the kind

of problems they must solve. The approach taken by this guide is unique in that the

particular languages and tools (e.g. assembly, C, Make, etc.) are not the focus but

instead are treated as a means to an end: we will learn what we need to about these

things to help us achieve our main goal.

1

CHAPTER 1. INTRODUCTION 2

This work is not intended as a replacement but rather as a stepping stone to excellent

work such as the Minix project [?] and to operating system development in general.

Chapter 2

Computer Architecture and the

Boot Process

2.1 The Boot Process

Now, we begin our journey.

When we reboot our computer, it must start up again, initially without any notion of

an operating system. Somehow, it must load the operating system --- whatever variant

that may be --- from some permanent storage device that is currently attached to the

computer (e.g. a floppy disk, a hard disk, a USB dongle, etc.).

As we will shortly discover, the pre-OS environment of your computer offers little in

the way of rich services: at this stage even a simple file system would be a luxury (e.g.

read and write logical files to a disk), but we have none of that. Luckily, what we do have

is the Basic Input/Output Software (BIOS), a collection of software routines that are

initially loaded from a chip into memory and initialised when the computer is switched

on. BIOS provides auto-detection and basic control of your computer’s essential devices,

such as the screen, keyboard, and hard disks.

After BIOS completes some low-level tests of the hardware, particularly whether or

not the installed memory is working correctly, it must boot the operating system stored

on one of your devices. Here, we are reminded, though, that BIOS cannot simply load a

file that represents your operating system from a disk, since BIOS has no notion of a file-

system. BIOS must read specific sectors of data (usually 512 bytes in size) from specific

physical locations of the disk devices, such as Cylinder 2, Head 3, Sector 5 (details of

disk addressing are described later, in Section XXX).

So, the easiest place for BIOS to find our OS is in the first sector of one of the disks

(i.e. Cylinder 0, Head 0, Sector 0), known as the boot sector. Since some of our disks may

not contain an operating systems (they may simply be connected for additional storage),

then it is important that BIOS can determine whether the boot sector of a particular

disk is boot code that is intended for execution or simply data. Note that the CPU does

not differentiate between code and data: both can be interpreted as CPU instructions,

where code is simply instructions that have been crafted by a programmer into some

useful algorithm.

3

CHAPTER 2. COMPUTER ARCHITECTURE AND THE BOOT

PROCESS 4

Again, an unsophisticated means is adopted here by BIOS, whereby the last two

bytes of an intended boot sector must be set to the magic number 0xaa55. So, BIOS

loops through each storage device (e.g. floppy drive, hard disk, CD drive, etc.), reads

the boot sector into memory, and instructs the CPU to begin executing the first boot

sector it finds that ends with the magic number.

This is where we seize control of the computer.

2.2 BIOS, Boot Blocks, and the Magic

Number

If we use a binary editor, such as TextPad [?] or GHex [?], that will let us write raw byte

values to a file --- rather than a standard text editor that will convert characters such as

’A’ into ASCII values --- then we can craft ourselves a simple yet valid boot sector.

e9 fd ff 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

*

00 00 00 00 00 00 00 00 00 00 00 00 00 00 55 aa

Figure 2.1: A machine code boot sector, with each byte displayed in

hexadecimal.

Note that, in Figure 2.1, the three important features are:

• The initial three bytes, in hexadecimal as 0xe9, 0xfd and 0xff, are actually

machine code instructions, as defined by the CPU manufacturer, to perform an

endless jump.

• The last two bytes, 0x55 and 0xaa, make up the magic number, which tells BIOS

that this is indeed a boot block and not just data that happens to be on a drive’s

boot sector.

• The file is padded with zeros (’*’ indicates zeros omitted for brevity), basically to

position the magic BIOS number at the end of the 512 byte disk sector.

An important note on endianness. You might be wondering why the magic BIOS

number was earlier described as the 16-bit value 0xaa55 but in our boot sector was

written as the consecutive bytes 0x55 and 0xaa. This is because the x86 architecture

handles multi-byte values in little-endian format, whereby less significant bytes proceed

more significant bytes, which is contrary to our familiar numbering system --- though if

our system ever switched and I had £0000005 in my bank account, I would be able to

retire now, and perhaps donate a couple of quid to the needy Ex-millionaires Foundation.

Compilers and assemblers can hide many issues of endianness from us by allowing

us to define the types of data, such that, say, a 16-bit value is serialised automatically

into machine code with its bytes in the correct order. However, it is sometimes useful,

CHAPTER 2. COMPUTER ARCHITECTURE AND THE BOOT

PROCESS 5

especially when looking for bugs, to know exactly where an individual byte will be stored

on a storage device or in memory, so endianness is very important.

This is possibly the smallest program your computer could run, but it is a valid

program nonetheless, and we can test this in two ways, the second of which is much safer

and better suited to our kind of experiments:

• Using whatever means your current operating system will allow, write this boot

block to the first sector of a non-essential storage device (e.g. floppy disk or flash

drive), then reboot the computer.

• Use virtual machine software, such as VMWare or VirtualBox, and set the boot

block code as a disk image of a virtual machine, then start-up the virtual machine.

You can be sure this code has been loaded and executed if your computer simply

hangs after booting, without a message such as “No operating system found”. This is the

infinite loop at work, that we put at the start of the code. Without this loop the CPU

would tear off, executing every subsequent instruction in memory, most of which will

be random, uninitialised bytes, until it throws itself into some invalid state and either

reboots or, by chance, stumbles upon and runs a BIOS routine that formats your main

disk.

Remember, it is us that program the computer, and the computer follows our in-

structions blindly, fetching and executing them, until it is switched off; so we need to

make sure that it executes our crafted code rather than random bytes of data held some-

where in memory. At this low level, we have a lot of power and responsibility over our

computer, so we need to learn how to control it.

2.3 CPU Emulation

There is a third, more convenient option for testing these low-level programs without

continuously having to reboot a machine or risk scrubbing your important data off a

disk, and that is to use a CPU emulator such as Bochs or QEmu. Unlike machine

virtualisation (e.g. VMware, VirtualBox), which tries to optimise for performance and

therefore usage of the hosted operating system by running guest instructions directly on

the CPU, emulation involves a program that behaves like a specific CPU architecture,

using variables to represent CPU registers and high-level control structures to simulate

lower level jumps and so on, so is much slower but often better suited for development

and debugging such systems.

Note that, in order to do anything useful with an emulator, you need to give it some

code to run in the form of a disk image file. An image file simply is the raw data (i.e.

machine code and data) that would otherwise have been written to medium of a hard

disk, a floppy disk, a CDROM, USB stick, etc. Indeed, some emulators will successfully

boot and run a real operating system from an image file downloaded or extracted from

an installation CDROM --- though virtualisation is better suited to this kind of use.

The emulators translate low-level display device instructions into pixel rendering on

a desktop window, so you can see exactly what would be rendered on a real monitor.

In general, and for the exercises in this document, it follows that any machine code

that runs correctly under an emulator will run correctly on the real architecture ---

though obviously must faster.

CHAPTER 2. COMPUTER ARCHITECTURE AND THE BOOT

PROCESS 6

2.3.1 Bochs: A x86 CPU Emulator

Bochs requires that we set up a simple configuration file, bochsrc, in the local directory,

that describes details of how real devices (e.g. the screen and keyboard) are to be

emulated and, importantly, which floppy disk image is to be booted when the emulated

computer starts.

Figure 2.2 shows a sample Bochs configuration file that we can use to test the boot

sector written in Section XXX and saved as the file boot sect.bin

# Tell bochs to use our boot se ctor code as tho ugh it were

# a fl oppy disk inse rted into a com put er at boot time .

flop pya : 1 _44 = b oot _se ct .bin , statu s = ins ert ed

boot : a

Figure 2.2: A simple Bochs configuration file.

To test our boot sector in Bochs, simply type:

$bochs

As a simple experiment, try changing the BIOS magic number in our boot sector to

something invalid then re-running Bochs.

Since Bochs’ emulation of a CPU is close to the real thing, after you’ve tested code

in Bochs, you should be able to boot it on a real machine, on which it will run much

faster.

2.3.2 QEmu

QEmu is similar to Bochs, though is much more efficient and capable also of emulating

architectures other than x86. Though QEmu is less well documented than Bochs, a need

for no configuration file means it is easier to get running, as follows:

$qemu <your-os-boot-disk-image-file>

2.4 The Usefulness of Hexadecimal

Notation

We’ve already seen some examples of hexadecimal, so it is important to understand why

hexadecimal is often used in lower-level programming.

First it may be helpful to consider why counting in ten seems so natural to us,

because when we see hexadecimal for the first time we always ask ourselves: why not

simply count to ten? Not being an expert on the matter, I will make the assumption that

counting to ten has something to do with most people having a total of ten fingers on

their hands, which led to the ideas of numbers being represented as 10 distinct symbols:

0,1,2,...8,9

CHAPTER 2. COMPUTER ARCHITECTURE AND THE BOOT

PROCESS 7

Decimal has a base of ten (i.e. has ten distinct digit symbols), but hexadecimal has

a base of 16, so we have to invent some new number symbols; and the lazy way is just to

use a few letters, giving us: 0,1,2,...8,9,a,b,c,d,e,f, where the single digit d, for

example, represents a count of 13.

To distinguish among hexadecimal and other number systems, we often use the prefix

0x, or sometimes the suffix h, which is especially important for hexadecimal digits that

happen not to contain any of the letter digits, for example: 0x50 does not equal (decimal)

50 --- 0x50 is actually 80 in decimal.

The thing is, that a computer represent a number as a sequence of bits (binary digits),

since fundamentally its circuitry can distinguish between only two electrical states: 0 and

1 --- it’s like the computer has a total of only two fingers. So, to represent a number

larger than 1, the computer can bunch together a series of bits, just like we may count

higher than 9 by having two or more digits (e.g. 456, 23, etc.).

Names have been adopted for bit series of certain lengths to make it easier to talk

about and agree upon the size of numbers we are dealing with. The instructions of

most computers deal with a minimum of 8 bit values, which are named bytes. Other

groupings are short, int, and long, which usually represent 16-bit, 32-bit, and 64-bit

values, respectively. We also see the term word, that is used to describe the size of the

maximum processing unit of the current mode of the CPU: so in 16-bit real mode, a

word refers to a 16-bit value; in 32-bit protected mode, a word refers to a 32-bit value;

and so on.

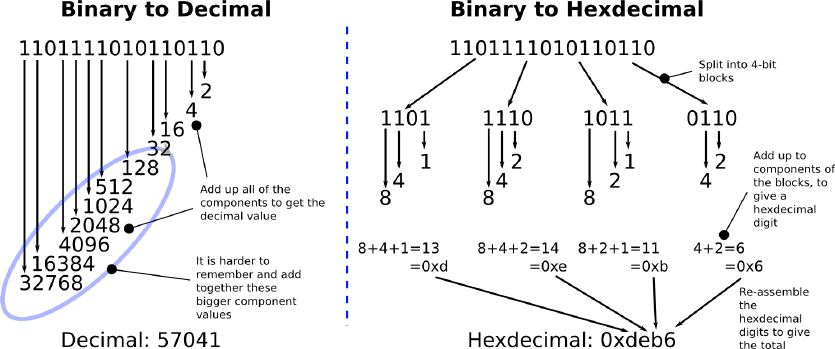

So, returning to the benefit of hexadecimal: strings of bits are rather long-winded to

write out but are much easier to convert to and from the more shorthand hexadecimal

notation than to and from our natural decimal system, essentially because we can break

the conversion down into smaller, 4-bit segments of the binary number, rather than try

to add up all of the component bits into a grand total, which gets much harder for larger

bit strings (e.g. 16, 32, 64, etc.). This difficulty with decimal conversion is shown clearly

by the example given in Figure 2.3.

Figure 2.3: Conversion of 1101111010110110 to decimal and hexadecimal

Chapter 3

Boot Sector Programming (in

16-bit Real Mode)

Even with the example code provided, you will no doubt have found it frustrating writing

machine code in a binary editor. You’d have to remember, or continuously reference,

which of many possible machine codes cause the CPU to do certain functions. Luckily,

you are not alone, and so assemblers have been written that translate more human

friendly instructions into machine code for a particular CPU.

In this chapter we will explore some increasingly sophisticated boot sector programs

to familiarise ourselves with assembly and the barren, pre-OS environment in which our

programs will run.

3.1 Boot Sector Re-visited

Now, we will re-create the binary-edited boot sector from Section XXX instead using

assembly language, so that we can really appreciate the value even of a very low-level

language.

We can assemble this into actual machine code (a sequence of bytes that our CPU

can interpret as instructions) as follows:

$nasm boot sect.asm -f bin -o boot sect.bin

Where boot sect.asm is the file into which we saved the source code in Figure 3.1

and boot sect.bin is the assembled machine code that we can install as a boot sector

on a disk.

Note that we used the -f bin option to instruct nasm to produce raw machine code,

rather than a code package that has additional meta information for linking in other rou-

tines that we would expect to use when programming in a more typical operating system

environment. We need none of that cruft. Apart from the low-level BIOS routines, we

are the only software running on this computer now. We are the operating system now,

albeit at this stage with nothing more to offer than an endless loop --- but we will soon

build up from this.

8

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 9

;

; A si mple boot sector pr o gram that loops for eve r.

;

loop : ; D efine a label , " loop " , that will allow

; us to jump back to it , fo reve r.

jmp loop ; Use a si mple CPU in st ruc tio n that ju mps

; to a new memory ad dres s to co nti nue ex ecu tio n.

; In our case , jump to the ad dres s of the cu rren t

; ins tr uct io n.

times 510 -($ - $$ ) db 0 ; When compiled , our progr am must fit into 512 bytes ,

; with the last two bytes being the magic number ,

; so here , tell our as semb ly co mpil er to pad out our

; p rogr am with e nough zero bytes ( db 0) to b ring us to the

; 510 th byte.

dw 0 xaa55 ; Last two bytes ( one word ) form the magic number ,

; so BIOS k nows we are a boot sect or.

Figure 3.1: A simple boot sector written in assembly language.

Rather than saving this to the boot sector of a floppy disk and rebooting our machine,

we can conveniently test this program by running Bochs:

$bochs

Or, depending on our preference and on availability of an emulator, we could use

QEmu, as follows:

$qemu boot sect.bin

Alternatively, you could load the image file into virtualisation software or write it

onto some bootable medium and boot it from a real computer. Note that, when you

write an image file to some bootable medium, that does not mean you add the file to the

medium’s file system: you must use an appropriate tool to write directly to the medium

in a low-level sense (e.g. directly to the sectors of a disk).

If we’d like to see more easily exactly what bytes the assembler created, we can run

the following command, which displays the binary contents of the file in an easy-to-read

hexadecimal format:

$od -t x1 -A n boot sect.bin

The output of this command should look familiar.

Congratulations, you just wrote a boot sector in assembly language. As we will see,

all operating systems must start this way and then pull themselves up into higher level

abstractions (e.g. higher level languages, such as C/C++)

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 10

3.2 16-bit Real Mode

CPU manufacturers must go to great lengths to keep their CPUs (i.e. their specific

instruction set) compatible with earlier CPUs, so that older software, and in particular

older operating systems, can still run on the most modern CPUs.

The solution implemented by Intel and compatible CPUs is to emulate the oldest

CPU in the family: the Intel 8086, which had support for 16-bit instructions and no

notion of memory protection: memory protection is crucial for the stabilty of modern

operating systems, since it allows an operating system to restrict a user’s process from

accessing, say, kernel memory, which, whether done accidentally or on purpose, could

allow such a process to circumvent security mechanisms or even bring down the whole

system.

So, for backward compatibility, it is important that CPUs boot initially in 16-bit

real mode, requiring modern operating systems explicitly to switch up into the more

advanced 32-bit (or 64-bit) protected mode, but allowing older operating systems to

carry on, blissfully unaware that they are running on a modern CPU. Later on, we will

look at this important step from 16-bit real mode into 32-bit protected mode in detail.

Generally, when we say that a CPU is 16-bit, we mean that its instructions can work

with a maximum of 16-bits at once, for example: a 16-bit CPU will have a particular

instruction that can add two 16-bit numbers together in one CPU cycle; if it was neces-

sary for a process to add together two 32-bit numbers, then it would take more cycles,

that make use of 16-bit addition.

First we will explore this 16-bit real mode environment, since all operating systems

must begin here, then later we will see how to switch into 32-bit protected mode and the

main benefits of doing so.

3.3 Erm, Hello?

Now we are going to write a seemingly simple boot sector program that prints a short

message on the screen. To do this we will have to learn some fundamentals of how the

CPU works and how we can use BIOS to help us to manipulate the screen device.

Firstly, let’s think about what we are trying to do here. We’d like to print a character

on the screen but we do not know exactly how to communicate with the screen device,

since there may be many different kinds of screen devices and they may have different

interfaces. This is why we need to use BIOS, since BIOS has already done some auto

detection of the hardware and, evidently by the fact that BIOS earlier printed information

on the screen about self-testing and so on, so can offer us a hand.

So, next, we’d like to ask BIOS to print a character for us, but how do we ask BIOS

to do that? There are no Java libraries for printing to the screen --- they are a dream

away. We can be sure, however, that somewhere in the memory of the computer there

will be some BIOS machine code that knows how to write to the screen. The truth is

that we could possibly find the BIOS code in memory and execute it somehow, but this

is more trouble than it is worth and will be prone to errors when there are differences

between BIOS routine internals on different machines.

Here we can make use of a fundamental mechanism of the computer: interrupts.

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 11

3.3.1 Interrupts

Interrupts are a mechanism that allow the CPU temporarily to halt what it is doing and

run some other, higher-priority instructions before returning to the original task. An

interrupt could be raised either by a software instruction (e.g. int 0x10) or by some

hardware device that requires high-priority action (e.g. to read some incoming data from

a network device).

Each interrupt is represented by a unique number that is an index to the interrupt

vector, a table initially set up by BIOS at the start of memory (i.e. at physical address

0x0) that contains address pointers to interrupt service routines (ISRs). An ISR is simply

a sequence of machine instructions, much like our boot sector code, that deals with a

specific interrupt (e.g. perhaps to read new data from a disk drive or from a network

card).

So, in a nutshell, BIOS adds some of its own ISRs to the interrupt vector that

specialise in certain aspects of the computer, for example: interrupt 0x10 causes the

screen-related ISR to be invoked; and interrupt 0x13, the disk-related I/O ISR.

However, it would be wasteful to allocate an interrupt per BIOS routine, so BIOS

multiplexes the ISRs by what we could imagine as a big switch statement, based usually

on the value set in one of the CPUs general purpose registers, ax, prior to raising the

interrupt.

3.3.2 CPU Registers

Just as we use variables in a higher level languages, it is useful if we can store data tem-

porarily during a particular routine. All x86 CPUs have four general purpose registers,

ax, bx, cx, and dx, for exactly that purpose. Also, these registers, which can each hold

a word (two bytes, 16 bits) of data, can be read and written by the CPU with negligible

delay as compared with accessing main memory. In assembly programs, one of the most

common operations is moving (or more accurately, copying) data between these registers:

mov ax , 1234 ; st ore the deci mal numb er 1234 in ax

mov cx , 0 x2 34 ; st ore the hex numbe r 0 x234 in cx

mov dx , ’ t ’ ; st ore the ASCII code for l etter ’t ’ in dx

mov bx , ax ; copy the value of ax into bx , so now bx == 1234

Notice that the destination is the first and not second argument of the mov operation,

but this convention varies with different assemblers.

Sometimes it is more convenient to work with single bytes, so these registers let us

set their high and low bytes independently:

mov ax , 0 ; ax -> 0 x0000 , or in b inary 0 00 00 000 00 00 000 0

mov ah , 0 x56 ; ax -> 0 x5600

mov al , 0 x23 ; ax -> 0 x5623

mov ah , 0 x16 ; ax -> 0 x1623

[?]

3.3.3 Putting it all Together

So, recall that we’d like BIOS to print a character on the screen for us, and that we

can invoke a specific BIOS routine by setting ax to some BIOS-defined value and then

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 12

triggering a specific interrupt. The specific routine we want is the BIOS scrolling tele-

type routine, which will print a single character on the screen and advance the cursor,

ready for the next character. There is a whole list of BIOS routines published that show

you which interrupt to use and how to set the registers prior to the interrupt. Here, we

need interrupt 0x10 and to set ah to 0x0e (to indicate tele-type mode) and al to the

ASCII code of the character we wish to print.

;

; A si mple boot sector that prints a me ssag e to the sc reen using a BIOS rout ine.

;

mov ah , 0 x0e ; int 10/ ah = 0 eh -> scr oll ing t elet ype BIOS rout ine

mov al , ’ H ’

int 0 x10

mov al , ’ e ’

int 0 x10

mov al , ’ l ’

int 0 x10

mov al , ’ l ’

int 0 x10

mov al , ’ o ’

int 0 x10

jmp $ ; Jump to the c urre nt addr ess ( i.e. f orev er ) .

;

; P addi ng and magic BIOS numbe r.

;

times 510 -($ - $$ ) db 0 ; Pad the boot sect or out with zero s

dw 0 xaa55 ; Last two bytes form the magic number ,

; so BIOS k nows we are a boot sect or.

Figure 3.2:

Figure 3.2 shows the whole boot sector program. Notice how, in this case, we only

needed to set ah once, then just changed al for different characters.

b4 0 e b0 48 cd 10 b0 65 cd 10 b0 6 c cd 10 b0 6c

cd 10 b0 6 f cd 10 e9 fd ff 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

*

00 00 00 00 00 00 00 00 00 00 00 00 00 00 55 aa

Figure 3.3:

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 13

Just for completeness, Figure 3.3 shows the raw machine code of this boot sector.

These are the actual bytes that are telling the CPU exactly what to do. If you are

surprised by the amount of effort and understanding that is involved in writing such a

barely --- if at all --- useful program, then remember that these instructions map very

closely to the CPU’s circuitry, so necessarily they are very simple, but also very fast.

You are getting to know your computer now, as it really is.

3.4 Hello, World!

Now we are going to attempt a slightly more advanced version of the ’hello’ program,

that introduces a few more CPU fundamentals and an understanding of the landscape

of memory into which our boot sector gets plonked by BIOS.

3.4.1 Memory, Addresses, and Labels

We said earlier how the CPU fetches and executes instructions from memory, and how it

was BIOS that loaded our 512-byte boot sector into memory and then, having finished

its initialisations, told the CPU to jump to the start of our code, whereupon it began

executing our first instruction, then the next, then the next, etc.

So our boot sector code is somewhere in memory; but where? We can imagine the

main memory as long sequence of bytes that can individually be accessed by an address

(i.e. an index), so if we want to find out what is in the 54th byte of memory, then 54 is

our address, which is often more convenient to express in hexadecimal: 0x36.

So the start of our boot-sector code, the very first machine code byte, is at some

address in memory, and it was BIOS that put us there. We might assume, unless we

knew otherwise, that BIOS loaded our code at the start of memory, at address 0x0. It’s

not so straightforward, though, because we know that BIOS has already being doing

initialisation work on the computer long before it loaded our code, and will actually

continue to service hardware interrupts for the clock, disk drives, and so on. So these

BIOS routines (e.g. ISRs, services for screen printing, etc.) themselves must be stored

somewhere in memory and must be preserved (i.e. not overwritten) whilst they are

still of use. Also, we noted earlier that the interrupt vector is located at the start of

memory, and were BIOS to load us there, our code would stomp over the table, and upon

the next interrupt occurring, the computer will likely crash and reboot: the mapping

between interrupt number and ISR would effectively have been severed.

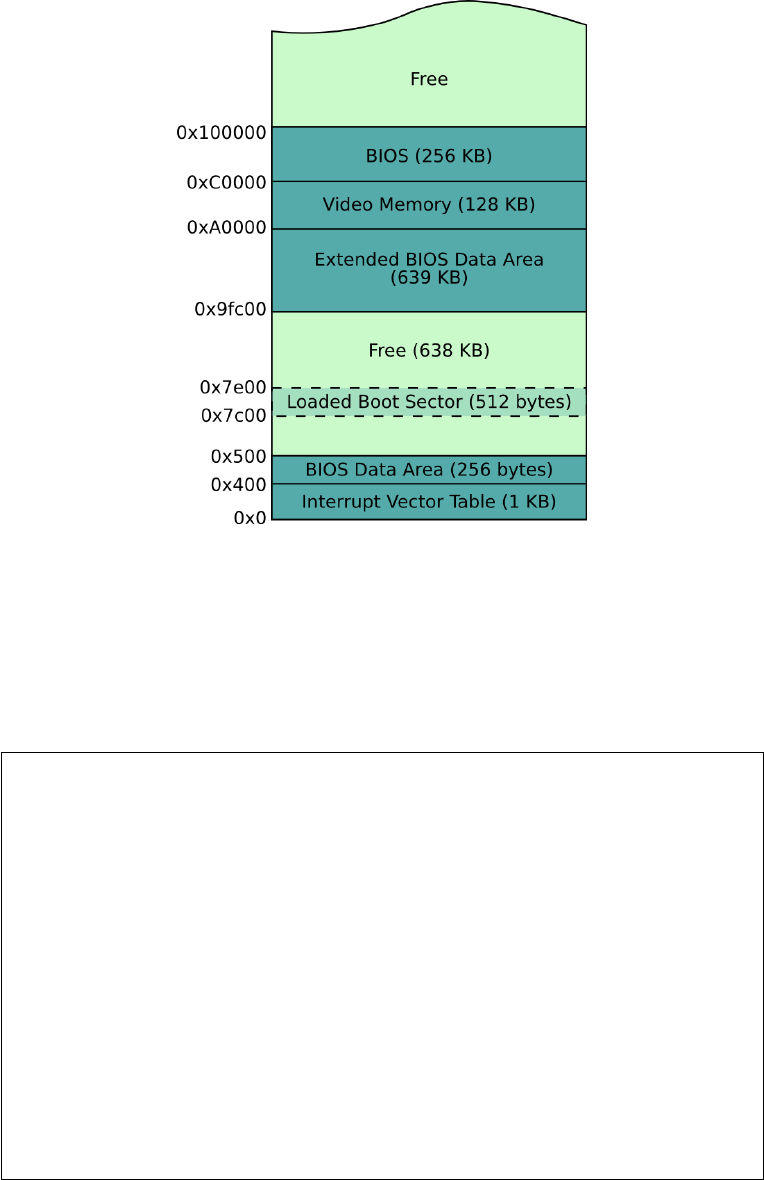

As it turns out, BIOS likes always to load the boot sector to the address 0x7c00,

where it is sure will not be occupied by important routines. Figure 3.4 gives an example

of the typical low memory layout of the computer when our boot sector has just been

loaded [?]. So whilst we may instruct the CPU to write data to any address in memory,

it may cause bad things to happen, since some memory is being used by other routines,

such as the timer interrupt and disk devices.

3.4.2 ’X’ Marks the Spot

Now we are going to play a game called “find the byte”, which will demonstrate memory

referencing, the use of labels in assembly code, and the importance of knowing where

BIOS loaded us to. We are going to write an assembly program that reserves a byte of

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 14

Figure 3.4: Typical lower memory layout after boot.

data for a character, then we will try to print out that character on the screen. To do

this we need to figure out its absolute memory address, so we can load it into al and get

BIOS to print it, as in the last exercise.

;

; A si mple boot sector pr o gram that de mon st rat es a ddr ess ing .

;

mov ah , 0 x0e ; int 10/ ah = 0 eh -> sc rol lin g tele type BIOS rou tine

; Fi rst atte mpt

mov al , t he_ sec ret

int 0 x10 ; Does this p rint an X?

; S econd at temp t

mov al , [ the _se cre t ]

int 0 x10 ; Does this p rint an X?

; Th ird atte mpt

mov bx , t he_ sec ret

add bx , 0 x7c00

mov al , [ bx ]

int 0 x10 ; Does this p rint an X?

; F ourth at temp t

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 15

mov al , [0 x7c1e ]

int 0 x10 ; Does this p rint an X?

jmp $ ; Jump fore ver .

the _se cre t :

db " X "

; P addi ng and magic BIOS numbe r.

times 510 -($ - $$ ) db 0

dw 0 xaa55

Firstly, when we declare some data in our program, we prefix it with a label (the secret).

We can put labels anywhere in our programs, with their only purpose being to give us a

convenient offset from the start of the code to a particular instruction or data.

b4 0 e b0 1 e cd 10 a0 1e 00 cd 10 bb 1e 00 81 c3

00 7 c 8a 07 cd 10 a0 1e 7 c cd 10 e9 fd ff 58 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

*

00 00 00 00 00 00 00 00 00 00 00 00 00 00 55 aa

Figure 3.5:

If we look at the assembled machine code in Figure 3.5, we can see that our ’X’,

which has an hexadecimal ASCII code 0x58, is at an offset of 30 (0x1e) bytes from the

start of the code, immediately before we padded the boot sector with zeros.

If we run the program we see that only the second two attempts succeed in printing

an ’X’.

The problem with the first attempt is that it tries to load the immediate offset into

al as the character to print, but actually we wanted to print the character at the offset

rather than the offset itself, as attempted next, whereby the square brackets instruct the

CPU to do this very thing - store the contents of an address.

So why does the second attempt fail? The problem is, that the CPU treats the offset

as though it was from the start of memory, rather than the start address of our loaded

code, which would land it around about in the interrupt vector. In the third attempt,

we add the offset the secret to the address that we beleive BIOS to have loaded our

code, 0x7c00, using the CPU add instruction. We can think of add as the higher level

language statement bx = bx + 0x7c00. We have now calculated the correct memory

address of our ’X’ and can store the contents of that address in al, ready for the BIOS

print function, with the instruction mov al, [bx].

In the fourth attempt we try to be a bit clever, by pre-calculating the address of the

’X’ after the boot sector is loaded into memory by BIOS. We arrive at the address 0x7c1e

based on our earlier examination of the binary code (See Figure 3.5) which revealed that

’X’ was 0x1e (30) bytes from the start of our boot sector. This last example reminds

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 16

us why labels are useful, since without labels we would have to count offsets from the

compiled code, and then update these when changes in code cause these offsets to change.

So now we have seen how BIOS does indeed load our boot sector to the address

0x7c00, and we have also seen how addressing and assembly code labels are related.

It is inconvenient to always have to account for this label--memory offset in your

code, so many assemblers will correct label references during assemblege if you include

the following instruction at the top of your code, telling it exactly where you expect the

code to loaded in memory:

[ org 0 x7c00 ]

Question 1

What do you expect will be printed now, when this org directive is added to this boot-

sector program? For good marks, explain why this is so.

3.4.3 Defining Strings

Supposing you wanted to print a pre-defined message (e.g. “Booting OS”) to the screen

at some point; how would you define such a string in your assembly program? We have

to remind ourselves that our computer knows nothing about strings, and that a string

is merely a sequence of data units (e.g. bytes, words, etc.) held somewhere in memory.

In the assembler we can define a string as follows:

my_ str ing :

db ’ Bo otin g OS ’

We’ve actually already seen db, which translates to “declare byte(s) of data”, which tells

the assembler to write the subsequent bytes directly to the binary output file (i.e. do not

interpret them as processor instructions). Since we surrounded our data with quotes,

the assembler knows to convert each character to its ASCII byte code. Note that, we

often use a label (e.g. my string) to mark the start of our data, otherwise we would

have no easy way of referencing it within our code.

One thing we have overlooked in this example is that knowing how long a string

is equally important as to knowing where it is. Since it is us that has to write all the

code that handles strings, it is important to have a consistent strategy for knowing how

long a string is. There are a few possibilities, but the convention is to declare strings

as null-terminating, which means we always declare the last byte of the string as 0, as

follows:

my_ str ing :

db ’ Bo otin g OS ’ ,0

When later iterating through a string, perhaps to print each of its characters in turn, we

can easily determine when we have reached the end.

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 17

3.4.4 Using the Stack

When on the topic of low-level computing, we often hear people talking about the stack

like it is some special thing. The stack is really just a simple solution to the following

inconvenience: the CPU has a limited number of registers for the temporary storage of

our routine’s local variables, but we often need more temporary storage than will fit into

these registers; now, we can obviously make use of main memory, but specifying specific

memory addresses when reading and writing is inconvenient, especially since we do not

care exactly where the data is to be stored, only that we can retrieve it easily enough.

And, as we shall see later, the stack is also useful for argument passing to realise function

calls.

So, the CPU offers two instructions push and pop that allow us, respectively, to store

a value and retrieve a value from the top of the stack, and so without worrying exactly

where they are stored. Note, however, that we cannot push and pop single bytes onto

and off the stack: in 16-bit mode, the stack works only on 16-bit boundaries.

The stack is implemented by two special CPU registers, bp and sp, which maintain

the addresses of the stack base (i.e. the stack bottom) and the stack top respectively.

Since the stack expands as we push data onto it, we usually set the stack’s base far away

from important regions of memory (e.g. such as BIOS code or our code) so their is no

danger of overwriting if the stack grows too large. One confusing thing about the stack

is that it actually grows downwards from the base pointer, so when we issue a push,

the value actually gets stored below --- and not above --- the address of bp, and sp is

decremented by the value’s size.

The following boot sector program in Figure 3.6 demonstrates use of the stack.

Question 2

What will be printed in what order by the code in Figure 3.6? And at what absolute

memory address will the ASCII character ’C’ be stored? You may find it useful to modify

the code to confirm your expectation, but be sure to explain why it is this address.

3.4.5 Control Structures

We’d never be comfortable using a programming language if we didn’t know how to

write some basic control structures, such as if..then..elseif..else, for, and while.

These structures allow alternative branches of execution and form the basis of any useful

routine.

After compilation, these high-level control structures reduce to simple jump state-

ments. Actually, we’ve already seen the simplest example of loops:

som e_l abe l :

jmp s ome _la bel ; jump to a ddre ss of lab el

Or alternatively, with identical effect:

jmp $ ; jump to a ddre ss of c urre nt in str uct io n

So this instruction offers us an unconditional jump (i.e. it will always jump); but we

often need to jump based on some condition (e.g. carry on looping until we have looped

ten times, etc.).

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 18

;

; A si mple boot sector pr o gram that de mon st rat es the sta ck.

;

mov ah , 0 x0e ; int 10/ ah = 0 eh -> scr oll ing t elet ype BIOS rout ine

mov bp , 0 x8000 ; Set the base of the stack a littl e above where BIOS

mov sp , bp ; loads our boot sector - so it won ’t ove rwr ite us.

push ’A ’ ; Push some c har act ers on the stack for later

push ’B ’ ; r etr eiv al. Note , thes e are p ushed on as

push ’C ’ ; 16 - bit values , so the most s ig nif ica nt byte

; will be added by our a sse mbl er as 0 x00.

pop bx ; Note , we can only pop 16 - bits , so pop to bx

mov al , bl ; the n copy bl ( i.e. 8 - bit char ) to al

int 0 x10 ; pr int ( al )

pop bx ; Pop the next value

mov al , bl

int 0 x10 ; pr int ( al )

mov al , [0 x7ffe ] ; To prove our stack grows d ownw ard s from bp ,

; fe tch the char at 0 x8000 - 0 x2 ( i.e. 16- bits )

int 0 x10 ; pr int ( al )

jmp $ ; Jump fo reve r.

; P addi ng and magic BIOS numbe r.

times 510 -($ - $$ ) db 0

dw 0 xaa55

Figure 3.6: Manipulation of the stack, using push and pop

Conditional jumps are achieved in assembly language by first running a comparison

instruction, then by issuing a specific conditional jump instruction.

cmp ax , 4 ; co mpar e the v alue in ax to 4

je the n_ blo ck ; j ump to th en_ blo ck if t hey were equal

mov bx , 45 ; oth erwise , exe cute this code

jmp th e_en d ; i mpo rta nt : jump over the ’ then ’ block ,

; so we don ’t also exec ute that code.

the n_b loc k :

mov bx , 23

the_ end :

In a language such as C or Java, this would look like this:

if( ax == 4) {

bx = 23;

} else {

bx = 45;

}

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 19

We can see from the assembly example that there is something going on behind the

scenes that is relating the cmp instruction to the je instruction it proceeds. This is an

example of where the CPU’s special flags register is used to capture the outcome of

the cmp instruction, so that a subsequent conditional jump instruction can determine

whether or not to jump to the specified address.

The following jump instructions are available, based on an earlier cmp x, y instruc-

tion:

je targe t ; jump if eq ual ( i.e. x == y )

jne tar get ; ju mp if not equal ( i.e. x != y)

jl targe t ; jump if less than (i .e. x < y)

jle tar get ; ju mp if less than or equal ( i.e. x <= y )

jg targe t ; jump if g reat er than ( i.e. x > y )

jge tar get ; ju mp if gre ater than or equa l ( i.e. x >= y )

Question 3

It’s always useful to plan your conditional code in terms of a higher level language, then

replace it with the assembly instructions. Have a go at converting this pseudo assembly

code into full assembly code, using cmp and appropriate jump instructions. Test it with

different values of bx. Fully comment your code, in your own words.

mov bx , 30

if ( bx <= 4) {

mov al , ’ A ’

} else if ( bx < 40) {

mov al , ’ B ’

} else {

mov al , ’ C ’

}

mov ah , 0 x0e ; int =10/ ah =0 x0e -> BIOS tele - type outpu t

int 0 x10 ; pri nt the char act er in al

jmp $

; P addi ng and magic num ber.

times 510 -($ - $$ ) db 0

dw 0 xaa55

3.4.6 Calling Functions

In high-level languages, we break big problems down into functions, which essentially

are general purpose routines (e.g. print a message, write to a file, etc.) that we use

over and over again throughout our program, usually changing parameters that we pass

to the function to change the outcome in some way. At the CPU level a function is

nothing more than a jump to the address of a useful routine then a jump back again to

the instruction immediately following the first jump.

We can kind of simulate a function call like this:

...

...

mov al , ’ H ’ ; St ore ’H ’ in al so our fu nct ion will p rint it.

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 20

jmp m y_ pri nt _f un ct ion

ret ur n_ to_ he re : ; T his la bel is our life - line so we can get bac k.

...

...

my _pr in t_ fu nct io n :

mov ah , 0 x0e ; int =10/ ah =0 x0e -> BIOS tele - type output

int 0 x10 ; pr int the cha rac t er in al

jmp r etu rn _t o_h er e ; retur n from the fu nct ion call.

Firstly, note how we used the register al as a parameter, by setting it up ready for

the function to use. This is how parameter passing is made possible in higher level

languages, where the caller and callee must have some agreement on where and how

many parameters will be passed.

Sadly, the main flaw with this approach is that we need to say explicitly where to

return to after our function has been called, and so it will not be possible to call this

function from arbitrary points in our program --- it will always return the same address,

in this case the label return to here.

Borrowing from the parameter passing idea, the caller code could store the correct

return address (i.e. the address immediately after the call) in some well-known location,

then the called code could jump back to that stored address. The CPU keeps track of the

current instruction being executed in the special register ip (instruction pointer), which,

sadly, we cannot access directly. However, the CPU provides a pair of instructions, call

and ret, which do exactly what we want: call behaves like jmp but additionally, before

actually jumping, pushes the return address on to the stack; ret then pops the return

address off the stack and jumps to it, as follows:

...

...

mov al , ’ H ’ ; St ore ’H ’ in al so our fu nct ion will p rint it.

call my_ pr in t_ fun ct io n

...

...

my _pr in t_ fu nct io n :

mov ah , 0 x0e ; int =10/ ah =0 x0e -> BIOS tele - type output

int 0 x10 ; pr int the cha rac t er in al

ret

Our functions are almost self-contained now, but there is a still an ugly problem that we

will thank ourselves later for if we now take the trouble to consider it. When we call a

function, such as a print function, within our assembly program, internally that function

may alter the values of several registers to perform its job (indeed, with registers being

a scarce resource, it will almost certainly do this), so when our program returns from

the function call it may not be safe to assume, say, the value we stored in dx will still be

there.

It is often sensible (and polite), therefore, for a function immediately to push any

registers it plans to alter onto the stack and then pop them off again (i.e. restore the

registers’ original values) immediately before it returns. Since a function may use many

of the general purpose registers, the CPU implements two convenient instructions, pusha

and popa, that conveniently push and pop all registers to and from the stack respectively,

for example:

...

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 21

...

som e_ fun ct ion :

pusha ; Push all re gist er valu es to the sta ck

mov bx , 10

add bx , 20

mov ah , 0 x0e ; int =10/ ah =0 x0e -> BIOS tele - type output

int 0 x10 ; pr int the cha rac t er in al

popa ; Rest ore or igin al reg ist er value s

ret

3.4.7 Include Files

After slaving away even on the seemingly simplest of assembly routines, you will likely

want to reuse your code in multiple programs. nasm allows you to include external files

literally as follows:

% i nclu de " my_ pr in t_ fu nc ti on .a sm " ; this will simply get re pla ced by

; the cont ents of the file

...

mov al , ’ H ’ ; St ore ’H ’ in al so our fu nct ion will p rint it.

call my_ pr in t_ fun ct io n

3.4.8 Putting it all Together

We now have enough knowledge about the CPU and assembly to write a more sophisti-

cated “Hello, World” boot sector program.

Question 4

Put together all of the ideas in this section to make a self-contained function for printing

null-terminated strings, that can be used as follows:

;

; A boot secto r that pri nts a strin g using our fun cti on.

;

[ org 0 x7c00 ] ; Tell the ass emb ler wher e this code will be loaded

mov bx , H ELL O_MS G ; Use BX as a p ara mete r to our function , so

call pri nt_ st rin g ; we can sp ecif y the addre ss of a st ring .

mov bx , G OOD BYE _M SG

call pri nt_ st rin g

jmp $ ; Hang

% i nclu de " pri nt _s tri ng .a sm "

; Data

HEL LO_ MSG :

db ’ Hello , Wo rld ! ’, 0 ; <-- The zero on the end tells our rout ine

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 22

; when to stop pr int ing ch ar act ers .

GOO DBY E_ MSG :

db ’ Go odby e ! ’ , 0

; P addi ng and magic num ber.

times 510 -($ - $$ ) db 0

dw 0 xaa55

For good marks, make sure the function is careful when modifying registers and that

you fully comment the code to demonstrate your understanding.

3.4.9 Summary

Still, it feels that we have not come very far. That’s okay, and that’s quite normal, given

the primitive environment that we have been working in. If you have understood all up

until here, then we are well on our way.

3.5 Nurse, Fetch me my Steth-o-scope

So far we have managed to get the computer to print out characters and strings that we

have loaded into memory, but soon we will be trying to load some data from the disk,

so it will be very helpful if we can display the hexadecimal values stored at aribitrary

memory addresses, to confirm if we have indeed managed to load anything. Remember,

we do not have the luxury of a nice development GUI, complete with a debugger that will

let us carefully step though and inspect our code, and the best feedback the computer

can give us when we make a mistake is visibly to do nothing at all, so we need to look

after ourselves.

We have already written a routine to print out a string of characters, so we will

now extend that idea into a hexadecimal printing routine --- a routine certainly to be

cherished in this unforgiving, low-level world.

Let’s think carefully about how we will do this, starting by considering how we’d like

to use the routine. In a high-level language, we’d like something like this: print hex(0x1fb6),

which would result in the string ’0x1fb6’ being printed on the screen. We have already

seen, in Section XXX, how functions can be called in assembly and how we can use

registers as parameters, so let’s use the dx register as a parameter to hold the value we

wish our print hex function to print:

mov dx , 0 x1fb6 ; s tore the value to pri nt in dx

call prin t_h ex ; call the func tion

; p rints the valu e of DX as hex .

pri nt_ hex :

...

...

ret

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 23

Since we are printing a string to the screen, we might as well re-use our earlier printing

function to do the actual printing part, then our main task is to look at how we can build

that string from the value in our parameter, dx. We definitely don’t want to confuse

matters more than we need to when working in assembly, so let’s consider the following

trick to get us started with this function. If we define the complete hexadecimal string as

a sort of template variable in our code, as we defined our earlier “Hello, World” messages,

we can simply get the string printing function to print it, then the task of our print hex

routine is to alter the components of that template string to reflect the hexadecimal

value as ASCII codes:

mov dx , 0 x1fb6 ; s tore the value to pri nt in dx

call prin t_h ex ; call the func tion

; p rints the valu e of DX as hex .

pri nt_ hex :

; TODO : man ipu lat e chars at H EX_O UT to r efle ct DX

mov bx , HE X_OU T ; pri nt the string po inte d to

call pri nt_ st rin g ; by BX

ret

; g lobal v aria ble s

HEX_ OUT : db ’0 x0000 ’ ,0

3.5.1 Question 5 (Advanced)

Complete the implementation of the print hex function. You may find the CPU instruc-

tions and and shr to be useful, which you can find information about on the Internet.

Make sure to fully explain your code with comments, in your own words.

3.6 Reading the Disk

We have now been introduced to BIOS, and have had a little play in the computer’s

low-level environment, but we have a little problem that poses to get in the way of our

plan to write an operating system: BIOS loaded our boot code from the first sector of

the disk, but that is all it loaded; what if our operating system code is larger --- and I’m

guessing it will be --- than 512 bytes.

Operating systems usually don’t fit into a single (512 byte) sector, so one of the first

things they must do is bootstrap the rest of their code from the disk into memory and

then begin executing that code. Luckily, as was hinted at earlier, BIOS provides routines

that allow us to manipulate data on the drives.

3.6.1 Extended Memory Access Using Segments

When the CPU runs in its intial 16-bit real mode, the maximum size of the registers is 16

bits, which means that the highest address we can reference in an instruction is 0xffff,

which amounts by today’s standards to a measily 64 KB (65536 bytes). Now, perhaps

the likes of our intended simple operating system would not be affected by this limit,

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 24

but a day-to-day operating systems would never sit comfortably in such a tight box, so

it is important that we understand the solution, of segmentation, to this problem.

To get around this limitation, the CPU designers added a few more special registers,

cs, ds, ss, and es, called segment registers. We can imagine main memory as being

divided into segments that are indexed by the segment registers, such that, when we

specify a 16-bit address, the CPU automatically calculates the absolute address as the

appropriate segment’s start address offseted by our specified address [?]. By appropriate

segment, I mean that, unless explicitly told otherwise, the CPU will offset our address

from the segment register appropriate for the context of our instruction, for example:

the address used in the instruction mov ax, [0x45ef] would by default be offset from

the data segment, indexed by ds; similarly, the stack segment, ss, is used to modify the

actual location of the stack’s base pointer, bp.

The most confusing thing about segment addressing is that adjacent segments overlap

almost completely but for 16 bytes, so different segment and offset combinations can

actually point to the same physical address; but enough of the talk: we won’t truly

grasp this concept until we’ve seen some examples.

To calculate the absolute address the CPU multiplies the value in the segment register

by 16 and then adds your offset address; and because we are working with hexadecimal,

when we multiple a number by 16, we simply shift it a digit to the left (e.g. 0x42 * 16

= 0x420). So if we set ds to 0x4d and then issue the statement mov ax, [0x20], the

value stored in ax will actually be loaded from address 0x4d0 (16 * 0x4d + 0x20).

Figure 3.7 shows how we can set ds to achieve a similar correction of label addressing

as when we used the [org 0x7c00] directive in Section XXX. Because we do not use the

org directive, the assmebler does not offset our labels to the correct memory locations

when the code is loaded by BIOS to the address 0x7c00, so the first attempt to print an

’X’ will fail. However, if we set the data segment register to 0x7c0, the CPU will do this

offset for us (i.e. 0x7c0 * 16 + the secret), and so the second attempt will correctly

print the ’X’. In the third and fourth attempts we do the same, and get the same results,

but instead explicitly state to the CPU which segment register to use when computing

the physical address, using instead the general purpose segment register es.

Note that limitations of the CPU’s circuitry (at least in 16-bit real mode) reveal

themselves here, when seemingly correct instructions like mov ds, 0x1234 are not actu-

ally possibly: just because we can store a literal address directly into a general purpose

register (e.g. mov ax, 0x1234 or mov cx, 0xdf), it doesn’t mean we can do the same

with every type of register, such as segment registers; and so, as in Figure 3.7, we must

take an additional step to transfer the value via a general purpose register.

So, segment-based addressing allows us to reach further into memory, up to a little

over 1 MB (0xffff * 16 + 0xffff). Later, we will see how more memory can be accessed,

when we switch to 32-bit protected mode, but for now it suffices for us to understand

16-bit real mode segment-based addressing.

3.6.2 How Disk Drives Work

Mechanically, hard disk drives contain one or more stacked platters that spin under a

read/write head, much like an old record player, only potentially, to increase capacity,

with several records stacked one above the other, where a head moves in and out to get

coverage of the whole of a particular spinning platter’s surface; and since a particular

platter may be readible and writable on both of its surfaces, one read/write head may

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 25

;

; A si mple boot sector pr o gram that de mon st rat es se gmen t offs et tin g

;

mov ah , 0 x0e ; int 10/ ah = 0 eh -> sc rol lin g tele type BIOS rou tine

mov al , [ the _se cre t ]

int 0 x10 ; D oes this print an X?

mov bx , 0 x7 c0 ; Can ’t set ds d irectly , so set bx

mov ds , bx ; then copy bx to ds.

mov al , [ the _se cre t ]

int 0 x10 ; D oes this print an X?

mov al , [ es : the_ sec re t ] ; Tell the CPU to use the es ( not ds ) s egm ent.

int 0 x10 ; D oes this print an X?

mov bx , 0 x7 c0

mov es , bx

mov al , [ es : the_ sec re t ]

int 0 x10 ; D oes this print an X?

jmp $ ; Jump fo reve r.

the _se cre t :

db " X "

; P addi ng and magic BIOS numbe r.

times 510 -($ - $$ ) db 0

dw 0 xaa55

Figure 3.7: Manipulating the data segment with the ds register.

float above and another below it. Figure 3.8 shows the inside of a typical hard disk

drive, with the stack of platters and heads exposed. Note that the same idea applies to

floppy disk drives, which, instead of several stacked hard platters, usually have a single,

two-sided floppy disk medium.

The metalic coating of the platters give them the property that specific areas of their

surface can be magnetised or demagnetised by the head, effectively allowing any state

to be recorded permanently on them [?]. It is therefore important to be able to describe

the exact place on the disk’s surface where some state is to be read or written, and

so Cylinder-Head-Sector (CHS) addressing is used, which effectively is a 3D coordinate

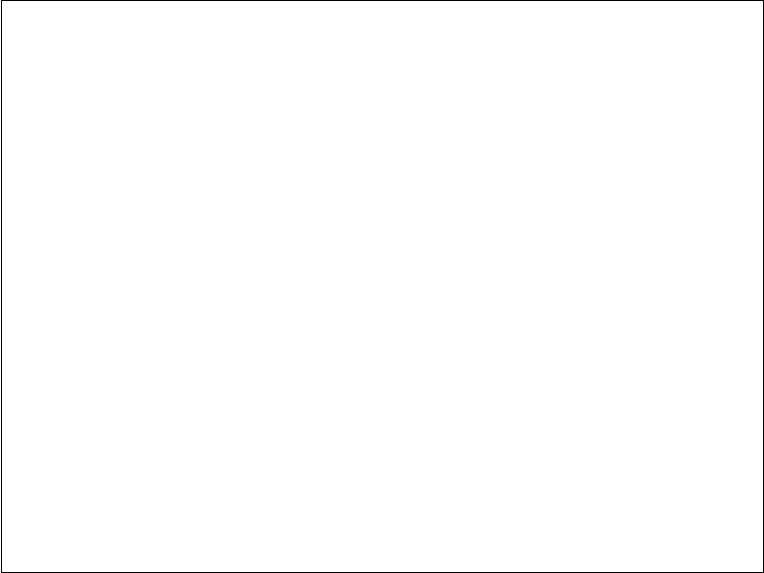

system (see Figure 3.9):

• Cylinder: the cylinder describes the head’s discrete distance from the outer edge

of the platter and is so named since, when several platters are stacked up, you

can visualise that all of the heads select a cylinder through all of the platters

• Head: the head describes which track (i.e. which specific platter surface within

the cylinder) we are interested in.

• Sector: the circular track is divided into sectors, usually of capacity 512 bytes,

which can be referenced with a sector index.

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 26

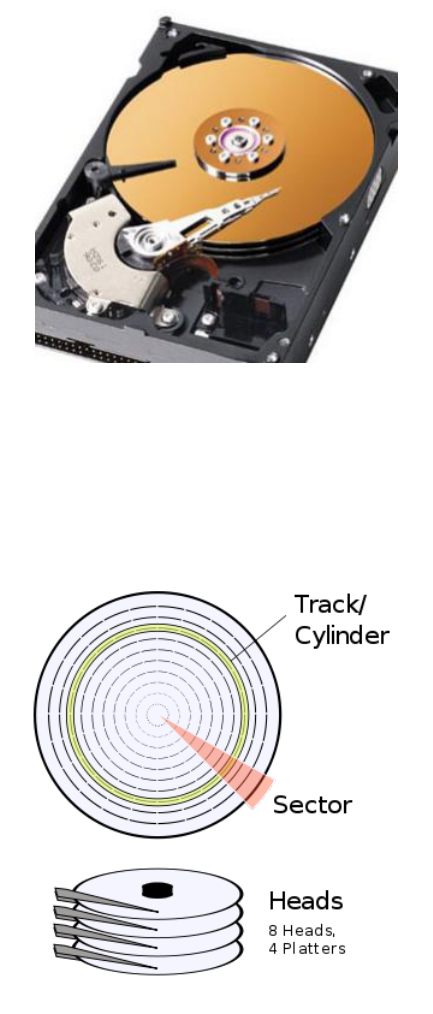

Figure 3.8: Inside of a hard disk drive

Figure 3.9: Cylinder, Head, Sector structure of a hard disk.

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 27

3.6.3 Using BIOS to Read the Disk

As we will see a little later on, specific devices require specific routines to be written

to use them, so, for example, a floppy disk device requires us to explicitly turn on and

off the motor that spins the disk under the read-and-write head before we can use it,

whereas most hard disk devices have more functionality automated on local chips [?], but

again the bus technologies with which such devices connect to the CPU (e.g. ATA/IDE,

SATA, SCSI, USB, etc.) affect how we access them. Thankfully, BIOS can offer a few

disk routines that abstract all of these differences for common disk devices.

The specific BIOS routine we are interested in here is accessed by raising interrupt

0x13 after setting the register al to 0x02. This BIOS routine expects us to set up a few

other registers with details of which disk device to use, which blocks we wish to read

from the disk, and where to store the blocks in memory. The most difficult part of using

this routine is that we must specify the first block to be read using a CHS addressing

scheme; otherwise, it is just a case of filling in the expected registers, as detailed in the

next code snippet.

mov ah , 0 x02 ; BIOS read sector fu nct ion

mov dl , 0 ; Read drive 0 ( i.e. first flo ppy drive )

mov ch , 3 ; S elect cy lin der 3

mov dh , 1 ; S elect the trac k on 2 nd side of flo ppy

; disk , sinc e this count has a bas e of 0

mov cl , 4 ; S elect the 4 th se ctor on the t rack - not

; the 5 th , sinc e this has a ba se of 1 .

mov al , 5 ; Read 5 sec tors from the start point

; Lastly , set the ad dres s th at we ’d like BI OS to r ead the

; s ecto rs to , whic h BIOS exp ects to find in ES : BX

; ( i.e. s egme nt ES with offs et BX ) .

mov bx , 0 xa000 ; Ind ire ctl y set ES to 0 x a 000

mov es , bx

mov bx , 0 x1234 ; Set BX to 0 x1234

; In our case , data wi ll be re ad to 0 xa0 00 :0 x1234 , which the

; CPU will tr ans lat e to ph ysi cal ad dres s 0 xa12 34

int 0 x13 ; Now is sue the BIOS i nte rru pt to do the actua l re ad.

Note that, for one reason or another (e.g. we indexed a sector beyond the limit of the

disk, an attempt was made to read a faulty sector, the floppy disk was not inserted into

the drive, etc.), BIOS may fail to read the disk for us, so it is important to know how

to detect this; otherwise, we may think we have read some data but in fact the target

address simply contains the same random bytes it did before we issued the read command.

Fortunately for us, BIOS updates some registers to let us know what happened: the carry

flag (CF) of the special flags register is set to signal a general fault, and al is set to the

number of sectors actually read, as opposed to the number requested. After issuing the

interrupt for the BIOS disk read, we can perform a simple check as follows:

...

...

int 0 x13 ; Is sue the BIOS i nte rru p t to do the actual read .

jc dis k_ err or ; jc is anot her jum ping ins tructi on , that j umps

; only if the carry flag was set.

; This jumps if what BIOS rep orte d as the nu mber of secto rs

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 28

; actu all y re ad in AL is not e qual to the n u mber we exp ect ed.

cmp al , < no. secto rs expected >

jne d isk _er ror

dis k_e rro r :

mov bx , D IS K_E RR OR_ MS G

call pri nt_ st rin g

jmp $

; G lobal v aria ble s

DIS K_ ER ROR _M SG : db " Disk read error !" , 0

3.6.4 Putting it all Together

As explained earlier, being able to read more data from the disk will be essential for boot-

strapping our operating system, so here we will put all of the ideas from this section into

a helpful routine that will simply read the first n sectors following the boot sector from

a specified disk device.

; load DH secto rs to ES : BX from drive DL

dis k_l oad :

push dx ; Store DX on stack so later we can r ecall

; how many sec tors were requ est to be read ,

; even if it is a lter ed in the meant ime

mov ah , 0 x02 ; BIOS read s ector f unct ion

mov al , dh ; Read DH secto rs

mov ch , 0 x00 ; S elect cy lin der 0

mov dh , 0 x00 ; S elect head 0

mov cl , 0 x02 ; St art readi ng from s econd sec tor ( i.e.

; af ter the boot se ctor )

int 0 x13 ; BIOS int err upt

jc dis k_ err or ; Jump if error ( i.e. car ry flag set )

pop dx ; R esto re DX from the stack

cmp dh , al ; if AL ( sect ors read ) != DH ( secto rs expe cte d )

jne d isk _er ror ; di spla y error mess age

ret

dis k_e rro r :

mov bx , D IS K_E RR OR_ MS G

call pri nt_ st rin g

jmp $

; Var iab les

DIS K_ ER ROR _M SG db " Disk read error !" , 0

And to test this routine, we can write a boot sector program as follows:

CHAPTER 3. BOOT SECTOR PROGRAMMING (IN 16-BIT REAL

MODE) 29

; Read some secto rs from the boot disk u sing our dis k_r ead fu nct ion

[ org 0 x7c00 ]

mov [ BOO T_D RIV E ] , dl ; BIOS stores our boot drive in DL , so it ’s

; best to reme mbe r this for lat er.

mov bp , 0 x8000 ; Here we set our sta ck s afely out of the

mov sp , bp ; way , at 0 x8000

mov bx , 0 x9000 ; Load 5 s ecto rs to 0 x0000 ( ES ):0 x9000 ( BX )

mov dh , 5 ; from the boot disk.

mov dl , [ BOO T_D RIV E ]

call disk _lo ad

mov dx , [0 x9000 ] ; Pr int out the first loade d word , whi ch

call prin t_h ex ; we expec t to be 0 xdada , stor ed

; at add ress 0 x9000

mov dx , [0 x9000 + 512] ; Also , pri nt the first wo rd from the

call prin t_h ex ; 2 nd load ed secto r : sho uld be 0 xface

jmp $

% i nclu de " .. / pri nt / pr in t_ str in g. as m " ; Re - use our pr in t_s tr ing f unct ion

% i nclu de " .. / hex / pr i nt _h ex. as m " ; Re - use our pri nt_ hex fu nct ion

% i nclu de " dis k_l oa d.a sm "

; I nclu de our new di sk_ loa d func tio n

; G lobal v aria ble s

BOO T_D RIV E : db 0

; Boo tse cto r padd ing

times 510 -($ - $$ ) db 0

dw 0 xaa55

; We know that BIOS will load only the fir st 512 - byte sector from the disk ,

; so if we pur pos ely add a few more sect ors to our code by rep eat ing some

; fami lia r numbers , we can pr ove to ou rse lfs that we ac tua lly loa ded those

; add iti ona l two sec tors from the disk we boote d from.

times 256 dw 0 xdada

times 256 dw 0 xface

Chapter 4

Entering 32-bit Protected Mode

It would be nice to continue working in the 16-bit real mode with which we have now

become much better aquainted, but in order to make fuller use of the CPU, and to

better understand how developments of CPU architecures can benefit modern operating

systems, namely memory protection in hardware, then we must press on into 32-bit

protected mode.

The main differences in 32-bit protected mode are:

• Registers are extended to 32 bits, with their full capacity being accessed by pre-

fixing an e to the register name, for example: mov ebx, 0x274fe8fe

• For convenience, there are two additional general purpose segment registers, fs

and gs.

• 32-bit memory offsets are available, so an offset can reference a whopping 4 GB

of memory (0xffffffff).

• The CPU supports a more sophisticated --- though slightly more complex ---

means of memory segmentation, which offers two big advantages:

– Code in one segment can be prohibited from executing code in a more priv-

ilidged segment, so you can protect your kernel code from user applications

– The CPU can implement virtual memory for user processes, such that pages

(i.e. fixed-sized chunks) of a process’s memory can be swapped transparently

between the disk and memory on an as-needed basis. This ensure main

memory is used efficiently, in that code or data that is rarely executed

needn’t hog valuable memory.

• Interrupt handling is also more sophisticated.

[?]

The most difficult part about switching the CPU from 16-bit real mode into 32-bit

protected mode is that we must prepare a complex data structure in memory called the

global descriptor table (GDT), which defines memory segments and their protected-mode

attributes. Once we have defined the GDT, we can use a special instruction to load it

30

CHAPTER 4. ENTERING 32-BIT PROTECTED MODE 31

into the CPU, before setting a single bit in a special CPU control register to make the

actual switch.

This process would be easy enough if we didn’t have to define the GDT in assembly

language, but sadly this low-level switch-over is unavoidable if we later wish to load a

kernel that has been compiled from a higher-level language such as C, which usually will

be compiled to 32-bit instructions rather than the less-efficient 16-bit instructions.

Oh, there is one shocker that I nearly forgot to mention: we can no longer use

BIOS once switched into 32-bit protected mode. If you thought making BIOS calls was

low-level. This is like one step backwards, two steps forwards.

4.1 Adapting to Life Without BIOS

It is true: in our quest to make full use of the CPU, we must abandon all of those helpful

routines provided by BIOS. As we will see when we look in more detail at the 32-bit

protected mode switch-over, BIOS routines, having been coded to work only in 16-bit

real mode, are no longer valid in 32-bit protected mode; indeed, attempting to use them

would likely crash the machine.

So what this means is that a 32-bit operating system must provide its own drivers for

all hardware of the machine (e.g. the keybaord, screen, disk drives, mouse, etc). Actually,

it is possible for a 32-bit protected mode operating system to switch temporarily back

into 16-bit mode whereupon it may utilise BIOS, but this teachnique can be more trouble

than it is worth, especially in terms of performance.

The first problem we will encounted in switching to protected mode is knowing how

to print a message on the screen, so we can see what is happening. Previously we

have asked BIOS to print an ASCII character on the screen, but how did that result in

the appropriate pixels being highlighted at the appropriate position of our computer’s

screen? For now, it suffices to know that the display device can be configured into one

of several resolutions in one of two modes, text mode and graphics mode; and that what

is displayed on the screen is a visual representation of a specific range of memory. So,

in order to manipulate the screen, we must manipulate the specific memory range that

it is using in its current mode. The display device is an example of memory-mapped

hardware because it works in this way.